## **PAN108** series

# User Manual

V1.9 Apr. 2024

Panchip Microelectronics Co., Ltd.

**BLE SoC Transceiver**

### **General Description**

PAN108 series integrates BLE5.3 and 2.4GHz dualmode wireless SoC transceiver. The wireless transceiver circuit works in the 2.400-2.483GHz universal ISM frequency band. There is an external 512KB/1MB Flash program memory and a built-in 64KB SRAM memory. In addition, PAN108 series is equipped with a wealth of peripherals, including up to 48 GPIOs, 24-channel PWM, three 32-bit timers, 1 I2C, 2 UARTs, 2 SPIs, 8 external channels ADC, WDT, WWDT, I2S master, I2S slave, USB2.0(Full Speed), 32K RC automatic calibration, QDEC and automatic key-scan, etc. PAN108 series is suitable for wireless mouse and keyboard, smart home and elec-tronic shelf label, BLE-AOA indoor locating.

#### **Key Features**

- MCU

- 32-bit MCU core running up to 64MHz

- Memory

- Build-in 512KB/1MB flash supporting deep sleep mode

- 64KB SRAM

- 256B eFuse

- 4 KB cache

- Low Power

- Active mode RX: 5.6mA(DCDC)

- Active mode TX at 0dBm: 6.1mA(DCDC)

- Standby mode : 0.34uA

- Standby mode(SRAM retention): 2uA(GPIO, XTL, RCL can wake up)

- Deep sleep mode: 8uA(All Logic Retention, GPIO, XTL, RCL can wake up)

- Clock

- 32MHz RC

- 32MHz XTAL

- 32kHz RC

- 32.768kHz XTAL

- DPLL(Two channels: 64MHz/48MHz and 48MHz (USB 2.0))

- RF

- Mode

- BLE5.3 modes:

- 1Mbps, 2Mbps, 500kbps, 125kbps

- 2.4G private protocol:

1Mbps / 2Mbps\_supporting hardw

- 1Mbps / 2Mbps, supporting hardware ACK

- Output power: -45dBm~7dBm

- Receiver

- -100dBm@125Kbps

- -99dBm@500Kbps

- -96dBm@1Mbps

- -93dBm@2Mbps

- RSSI

- Resolution: 0.25dB

- PAN108 series BLE SoC Transceiver

- Accuracy: ±2dB

- $\circ$  Range: 90dbm ~ -15dBm

- Positioning: AoA/AoD supported

- Single antenna supported

- Safety regulations: BQB / ETSI / FCC

- Peripheral

- Up to 48 GPIOs (there are two power supply voltages)

- 24-channel PWM

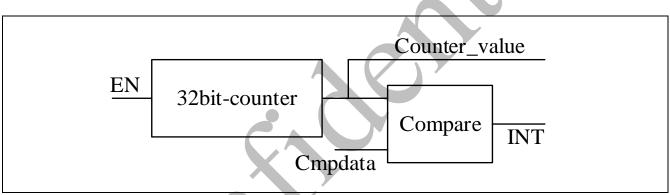

- Three 32-bit timer

- One I2C

- Two UARTs

- Two SPIs

- 3-channel DMA

- 11-channel ADC(8 ext, bandgap, VDD/4, temp)

- Two I2S(one I2S master and one I2S slave)

- 3-channel QDEC

- WDT / WWDT

- ECC accelerator

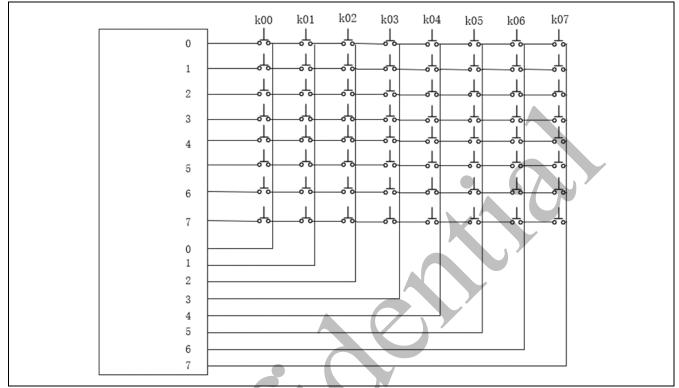

- Automatic key-scan

- IO / BOD / POR / LVR / System reset

- FMC(Support IAP, support the boot loader with address 0x0)

- Clock measurement and clock calibration

- USB2.0(Full\_speed)

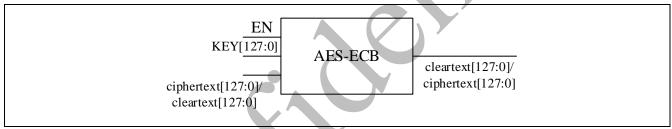

- Flash data encryption

- Temperature sensor

- Support temperature sensor

- Test range:  $-40^{\circ}$ C ~  $85^{\circ}$ C Accuracy:  $\pm 2^{\circ}$ C (With calibration)

- Power Management

- Integrated voltage regulator

- Operating voltage: 1.8V to 3.7V (Support DCDC)

- Package

- LQFP64 (7×7mm)

- QFN48 (6×6mm) / QFN32 (5×5mm)

- Operating Condition

- Operating temperature:

- $-40^{\circ}C \sim 85^{\circ}C / -40^{\circ}C \sim 125^{\circ}C / -40^{\circ}C \sim 105^{\circ}C$

- Storage temperature: -60°C~150°C

- ESD

- MM: ±250V(LQFP64) / ±250V(QFN48)/ ±300V(QFN32)

- CDM: ±500V

- Latch-up: ±500mA

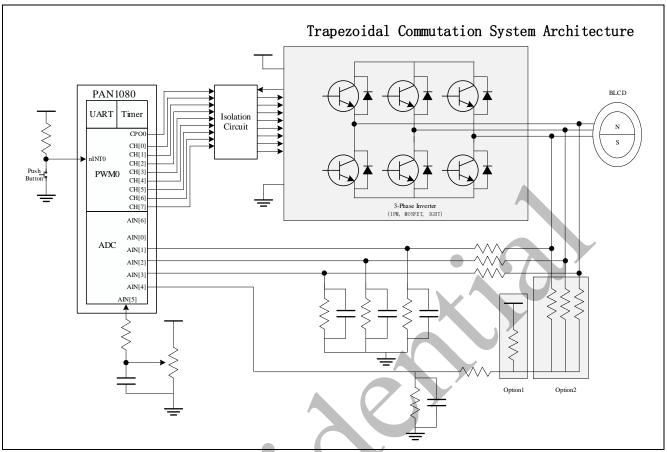

#### **Typical Applications**

- High-precision BLE-AOA in-door location system

- Electronic Shelf Label

- Wireless mouse and keyboard

- LED light control

. . .

#### **Bluetooth Features**

#### **Bluetooth Low Energy Controller**

The PAN108 series Bluetooth Low Energy Controller supports all low-energy features required by Bluetooth specification version 5.3. The controller supports the following:

- Support 1M PHY, 2M PHY and Coded PHY (s2 and s8)

- Support Advertising, Scanning, Initiating and Connection (both of Central and Periph-eral) role

- Up to 10 Link Layer state machines concurrently:

1 \* Passive Scanning

- 1 \* Non-connectable advertising

- 8 \* Any other combinations (Legacy/Extended/Periodic Adverstising, Scanning and Connection)

- Support LE Features:

- LL Encryption

- LE Data Packet Length Extension

- LL Privacy

- Extended Scanner Filter Policies

- LE Extended and Periodic Adverstising

- Channel Selection Algorithm #2

- Constant Tone Extension

- Support Update Channel Statistics

#### **Bluetooth Host**

- Generic Access Profile (GAP) with all possible LE roles

- Peripheral & Central

- Observer & Broadcaster

- GATT (Generic Attribute Profile)

- Server (to be a sensor)

- Client (to connect to sensors)

- Pairing support, including the Secure Connections feature from Bluetooth 4.2

- Non-volatile storage support for permanent storage of Bluetooth-specific settings and data

- PAN108 series BLE SoC Transceiver

- Clean HCI driver abstraction

- 3-Wire (H5) & 5-Wire (H4) UART

- SPI

- Local controller support as a virtual HCI driver

#### **Bluetooth Mesh**

- Compatible with Bluetooth SIG Mesh Profile 1.0.1

- Support Mesh Provisioning

- Provisioner: PB-ADV

- Provisionee: PB-ADV, PB-GATT and PB-Remote

- Support Mesh Node Feature : Relay, Proxy, Friend, LPN

- Support Mesh Models

- SIG Models: Config Model, Health Model and Generic Models (Onoff and Light Con-trol Models)

- SIG Developing Models: PB-Remote Model and SIG OTA Model

- Support multiple smart speakers control concurrently for BaiDu Xiaodu, Alibaba Aligenie and Amazon Echo

- Support network control: HeartBeat, Subnet, Secure Beacon and Group Control

- Support switch control for over 256 nodes without delay

- Mesh Security

- Provisioning: FIPS P-256 Elliptic Curve

- Message: AES-CCM Encryption

- Network: SEQ Control, IV Index and Key Fresh

### **Proprietary Radio 2.4G Features**

- Support 1M and 2M PHY

- XN297L,PAN1026 Transceiver protocol compliant

- Support No Acknowledge, Acknowledge and Acknowledge with payload

- Support CRC8, CRC16 and CRC24

- Support whitening

### Content

| Gen  | General Description |             |                                                               | 2 |      |

|------|---------------------|-------------|---------------------------------------------------------------|---|------|

| Key  | Featu               | res         |                                                               |   | 2    |

| Тур  | ical A              | pplications |                                                               |   | 2    |

| Blue | etooth              | Features    |                                                               |   | 3    |

|      | Blue                | tooth Low   | Energy Controller                                             |   | 3    |

|      | Blue                | tooth Host  |                                                               |   | 3    |

|      | Blue                | tooth Mes   | 1                                                             |   | 3    |

| Prop | orietary            | y Radio 2.4 | 4G Features                                                   |   | 3    |

| Con  | tent                |             |                                                               |   | 4    |

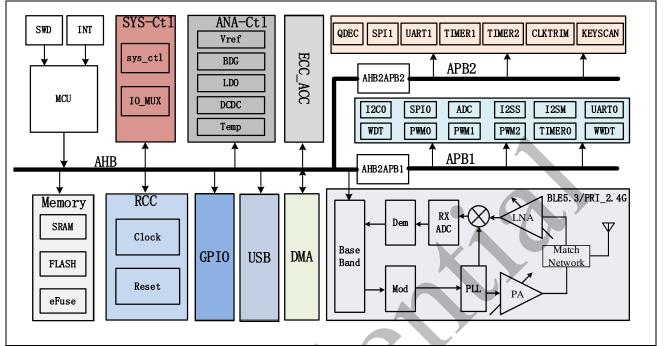

| 1    | Block               | Diagram     |                                                               |   | 24   |

| 2    | Pin Ir              | nformation  |                                                               |   | 25   |

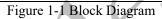

|      | 2.1                 | QFN 3       | 2-PIN Diagram                                                 |   | 25   |

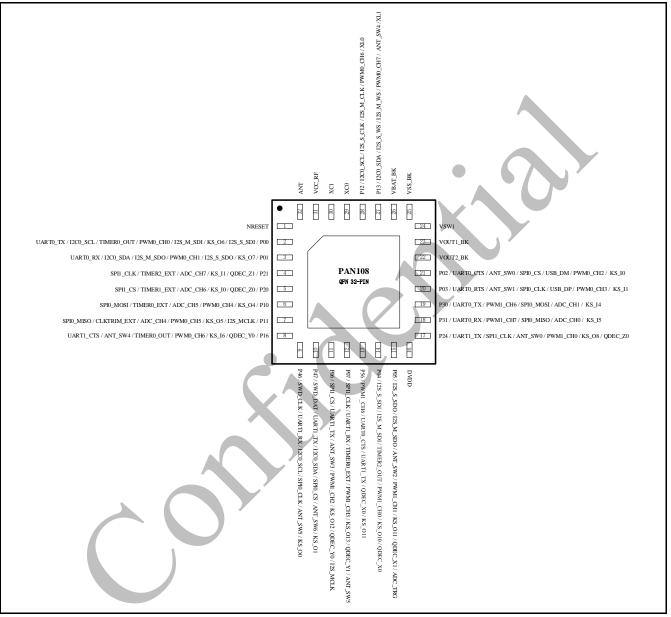

|      | 2.2                 | QFN 4       | 8-PIN Diagram                                                 |   | 26   |

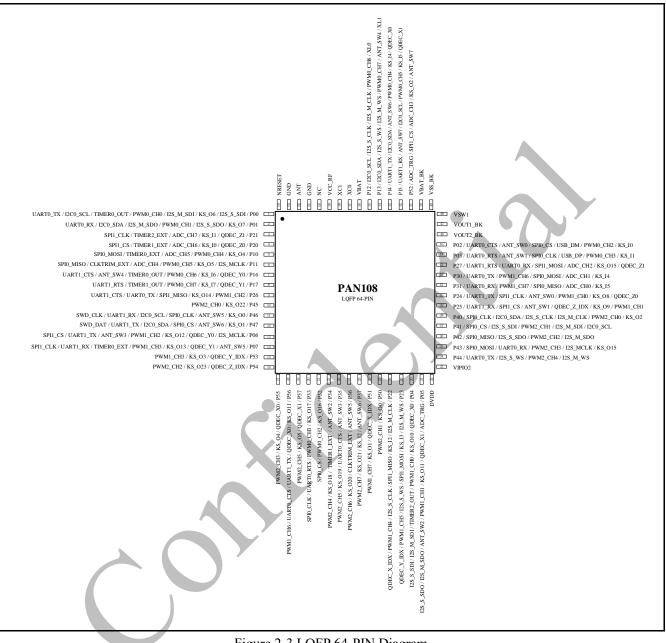

|      | 2.3                 |             | 64-PIN Diagram                                                |   |      |

|      | 2.4                 | Pin De      | scriptions                                                    |   | 28   |

| 3    | Funct               |             | ption                                                         |   |      |

|      | 3.1                 | Systen      | n Manager                                                     |   | 38   |

|      |                     | 3.1.1       | Overview                                                      |   | . 38 |

|      |                     | 3.1.2       | Memory Organization                                           |   | . 38 |

|      |                     | 3.1.        | 2.1 Overview                                                  |   | . 38 |

|      |                     | 3.1.        | 2.2 System Memory Map<br>System Register Map                  |   | . 38 |

|      |                     | 3.1.3       | System Register Map                                           |   | . 39 |

|      |                     | 3.1.4       | System Register Description                                   |   | . 40 |

|      |                     | 3.1.        | 4.1 Multiple Function Port0 Control Register (SYS_P0_MFP)     |   | . 40 |

|      |                     |             | 4.2 Multiple Function Port1 Control Register (SYS_P1_MFP)     |   |      |

|      |                     |             | 4.3 Multiple Function Port2 Control Register (SYS_P2_MFP)     |   |      |

|      |                     |             | 4.4 Multiple Function Port3 Control Register (SYS_P3_MFP)     |   |      |

|      |                     |             | 4.5 Multiple Function Port4 Control Register (SYS_P4_MFP)     |   |      |

|      |                     |             | 4.6 Multiple Function Port5 Control Register (SYS_P5_MFP)     |   |      |

|      |                     |             | 4.7 Register Write-Protection Control Register (SYS_REGLCTL). |   |      |

|      |                     | 3.1.        | 4.8 DMA Channel Select Control Register (SYS_CNTRL0)          |   | . 55 |

|      |                     | 3.1.5       | System Timer (SysTick)                                        |   | . 56 |

|      |                     |             | 5.1 System Timer Control Register Map                         |   |      |

|      |                     | 3.1.        | 5.2 System Timer Control Register Description                 |   |      |

|      |                     |             | SysTick Control and Status Register (SYST_CTRL)               |   |      |

|      |                     |             | SysTick Reload Value Register (SYST_LOAD)                     |   |      |

|      |                     |             | SysTick Current Value Register (SYST_VAL)                     |   | . 58 |

|      |                     | 3.1.6       | Nested Vectored Interrupt Controller (NVIC)                   |   |      |

|      |                     | 3.1.        | 6.1 Overview                                                  |   | . 59 |

|      |                     |             | 6.2 Features                                                  |   |      |

|      |                     |             | 6.3 Exception Model and System Interrupt Map                  |   |      |

|      |                     |             | 6.4 Vector Table                                              |   |      |

|      |                     |             | 6.5 Operation Description                                     |   |      |

|      |                     |             | 6.6 NVIC Control Register Map                                 |   |      |

|      |                     | 3.1.        | 6.7 NVIC Control Register Description                         |   |      |

|      |                     |             | IRQ0 ~ IRQ31 Set-Enable Control Register (NVIC_ISER)          |   |      |

|      |                     |             | IRQ0 ~ IRQ31 Clear-Enable Control Register (NVIC_ICER)        |   |      |

|      |                     |             | IRQ0 ~ IRQ31 Set-Pending Control Register (NVIC_ISPR)         |   |      |

|      |                     |             | IRQ0 ~ IRQ31 Clear-Pending Control Register (NVIC_ICPR)       |   |      |

|      |                     |             | IRQ0 ~ IRQ3 Interrupt Priority Register (NVIC_IPR0)           |   |      |

|      |                     |             | IRQ4 ~ IRQ7 Interrupt Priority Register (NVIC_IPR1)           |   |      |

|      |                     |             | IRQ8 ~ IRQ11 Interrupt Priority Register (NVIC_IPR2)          |   | . 66 |

|     | IRQ12 ~ IRQ15 Interrupt Priority Register (NVIC IPR3)        | 66  |

|-----|--------------------------------------------------------------|-----|

|     | IRQ16 ~ IRQ19 Interrupt Priority Register (NVIC IPR4)        |     |

|     | IRQ20 ~ IRQ23 Interrupt Priority Register (NVIC IPR5)        |     |

|     | IRQ24 ~ IRQ27 Interrupt Priority Register (NVIC IPR6)        |     |

|     | IRQ28 ~ IRQ31 Interrupt Priority Register (NVIC IPR7)        |     |

|     | 3.1.6.8 System Control Block Registers (SCB)                 |     |

|     | 3.1.6.9 System Control Block Register Map                    |     |

|     | 3.1.6.10 System Control Block Register Map                   |     |

|     | CPUID Base Register (SCS CPUID)                              |     |

|     |                                                              |     |

|     | Interrupt Control State Register (SCS_ICSR)                  |     |

|     | Application Interrupt and Reset Control Register (SCS_AIRCR) |     |

|     | System Control Register (SCS_SCR)                            |     |

|     | System Handler Priority Register 2 (SCS_SHPR2)               |     |

|     | System Handler Priority Register 3 (SCS_SHPR3)               |     |

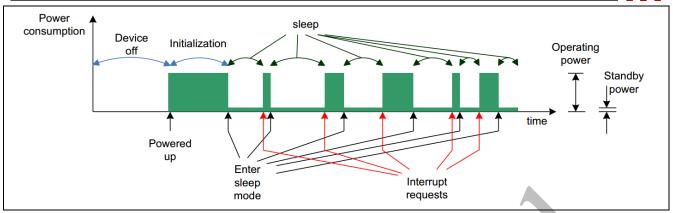

| 3.2 | Power Management                                             |     |

|     | 3.2.1 Overview                                               |     |

|     | 3.2.2 System Power                                           | 73  |

|     | 3.2.2.1 Power Supply<br>3.2.3 Low Power System               | 73  |

|     | 3.2.3 Low Power System                                       | 73  |

|     | 3.2.3.1 Low power system introduction                        | 73  |

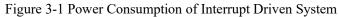

|     | 3.2.3.2 Low Power Mode of MCU                                | 74  |

|     | Sleep Mode                                                   | 74  |

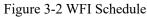

|     | WFI                                                          | 75  |

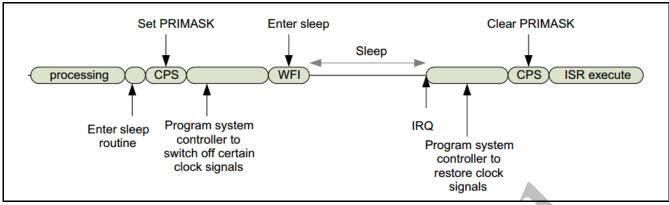

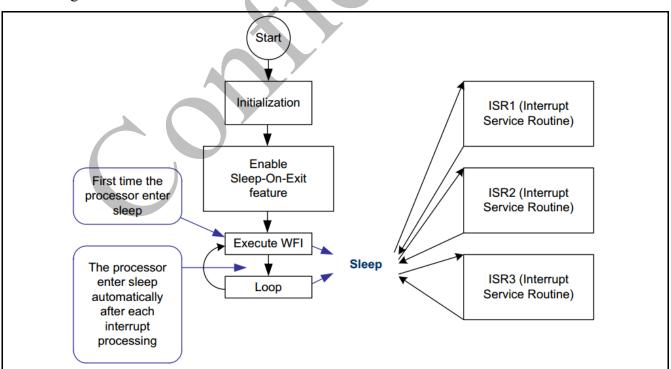

|     | Sleep-On-Exit Function                                       | 76  |

|     | 3.2.4 Low Power Mode                                         | 77  |

|     | 3.2.4.1 Power Modes and Wake-up Sources                      |     |

|     | Standby Mode                                                 |     |

|     | Deepsleep Mode                                               | 78  |

|     | Sleep Mode                                                   | 78  |

|     | 3.2.4.2 Operation Mode Switch Process                        |     |

|     | Enter and Exit Standby Mode                                  |     |

|     | Enter and Exit DeepSleep Mode                                |     |

|     | Enter and Exit Sleep Mode                                    |     |

|     |                                                              |     |

|     | Enter and Exit Standby Mode0 Timing                          |     |

|     | Enter and Exit DeepSleep Mode Timing                         |     |

|     | Enter and Exit Standby Mode1 Timing                          |     |

|     | 3.2.4.3 LP_WDT Instruction                                   |     |

|     | 3.2.4.4 LDO Instruction                                      |     |

|     | 3.2.4.5 Buck Instruction                                     |     |

|     | 3.2.5 Register Map                                           |     |

|     | 3.2.6 Register Description                                   |     |

|     | 3.2.6.1 LP_REG_SYNC                                          |     |

|     | 3.2.6.2 LP_FL_CTRL                                           |     |

|     | 3.2.6.3 LP_TMR_CTRL                                          |     |

|     | 3.2.6.4 LP_INT_CTRL                                          |     |

|     | 3.2.6.5 LP_RST_CTRL                                          |     |

|     | 3.2.6.6 LP_WDT_CNT                                           | 94  |

|     | 3.2.6.7LP_WDT_CTRL                                           | 95  |

|     | 3.2.6.8 LP PTAT POLY                                         | 96  |

|     | 3.2.6.9 LP HPLDO                                             |     |

|     | 3.2.6.10LP LPLDO                                             |     |

|     | 3.2.6.11 LP ANALDO                                           |     |

|     | 3.2.6.12 LP FSYNLDO                                          |     |

|     | 3.2.6.13 LP_SW                                               |     |

|     | 3.2.6.14 LP BUCK                                             |     |

|     | 3.2.6.15 LP MISC                                             |     |

|     |                                                              | 105 |

|     | 3.2.6.16 ANA ADCLDO                                                                                                 | 105  |

|-----|---------------------------------------------------------------------------------------------------------------------|------|

|     | 3.2.6.17 ANA RFFELDO                                                                                                |      |

|     | 3.2.6.18 ANA VCOLDO                                                                                                 |      |

|     | 3.2.6.19 ANA DFT                                                                                                    |      |

|     | 3.2.6.20 ANA TEMP                                                                                                   |      |

|     | 3.2.6.21 ANA MISC                                                                                                   |      |

|     | 3.2.6.22 ANA MISC2                                                                                                  |      |

|     | 3.2.6.23 ANA RESERVED                                                                                               |      |

| 3.3 | Reset and Clock Controller (RCC)                                                                                    |      |

| 5.5 |                                                                                                                     |      |

|     |                                                                                                                     |      |

|     | 3.3.2 Reset                                                                                                         |      |

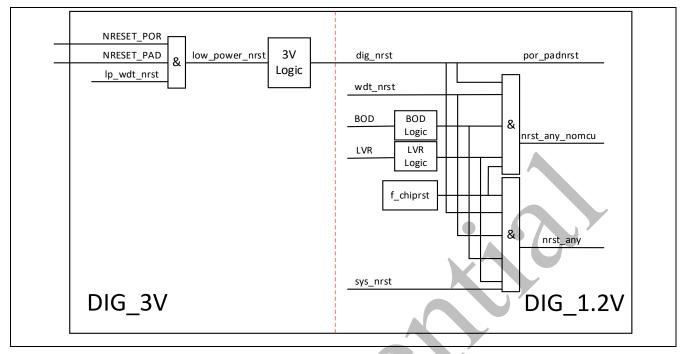

|     | 3.3.2.1 Reset Block Diagram                                                                                         |      |

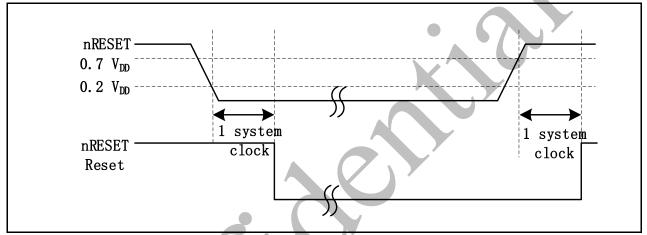

|     | 3.3.2.2 nRESET Reset                                                                                                |      |

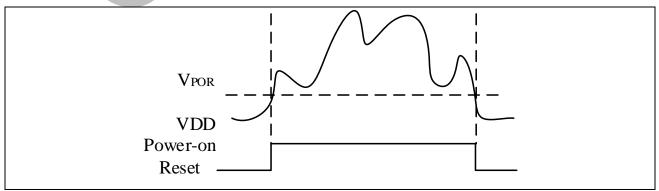

|     | 3.3.2.3 Power-On Reset (POR)                                                                                        |      |

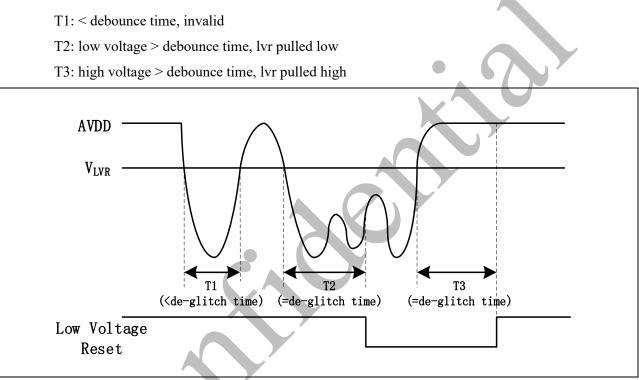

|     | 3.3.2.4 Low Voltage Reset (LVR)                                                                                     | .114 |

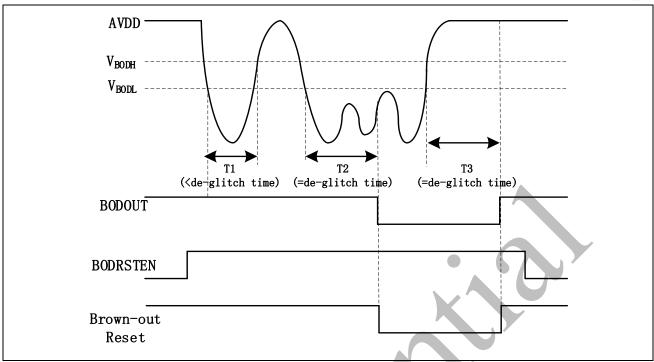

|     | 3.3.2.5 Brown-out Detector Reset (BOD Reset)                                                                        | .114 |

|     | 3.3.2.6 Watchdog Timer Reset                                                                                        | .115 |

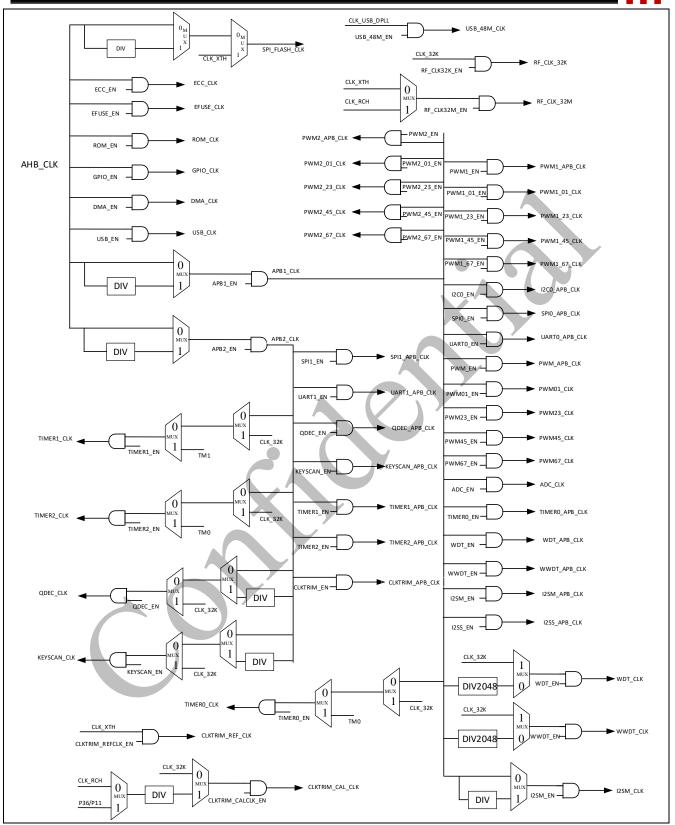

|     | 3.3.3 Clock Controller                                                                                              | .116 |

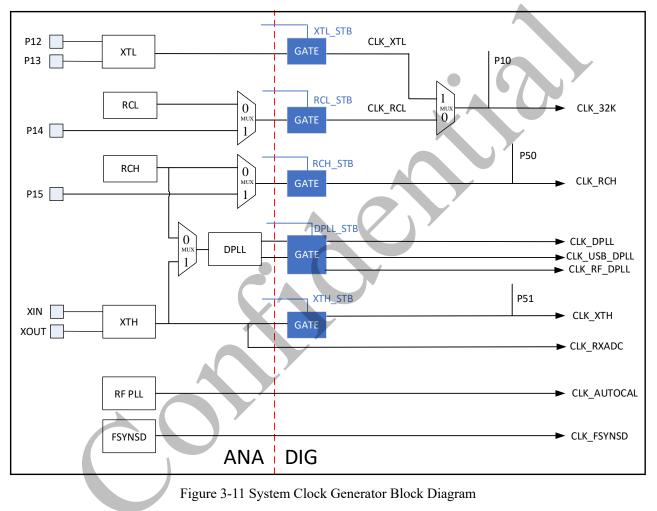

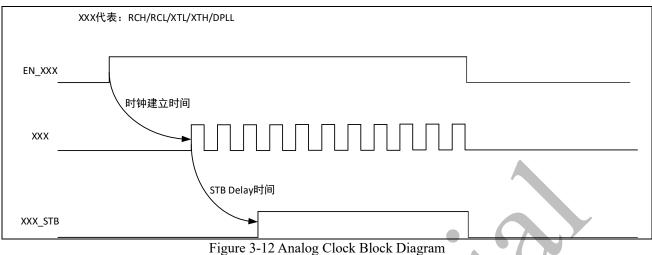

|     | 3.3.3.1 Analog Clock                                                                                                | .116 |

|     | Analog Clock Source                                                                                                 | .116 |

|     | Analog Clock Block Diagram                                                                                          | .117 |

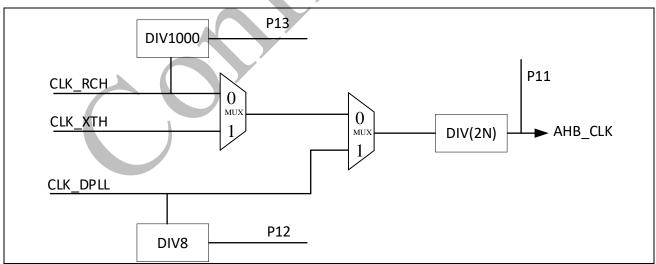

|     | 3.3.3.2 System Clock Block Diagram                                                                                  | .117 |

|     | 3.3.2 System Clock Block Diagram.         3.3.4       RCC Register Map         3.3.5       RCC Register Description | 120  |

|     | 3.3.5 RCC Register Description                                                                                      | 121  |

|     | 3.3.5.1 RSTSTS                                                                                                      | 121  |

|     | 3.3.5.2 IPRST0                                                                                                      |      |

|     | 3.3.5.3 IPRST1                                                                                                      | 123  |

|     | 3.3.5.4 BODCTL                                                                                                      | 124  |

|     | 3.3.5.5 BLDBCTL                                                                                                     | 120  |

|     | 3.5.5 BLDBCTL                                                                                                       | 120  |

|     | 3.3.5.6 Clock top control                                                                                           | 129  |

|     | 3.3.5.7 RCL_CTRL                                                                                                    | 130  |

|     | 3.3.5.8 RCH_CTRL                                                                                                    | 130  |

|     | 3.3.5.9 XTL Control (XTL_CTRL)                                                                                      | 130  |

|     | 3.3.5.10 XTH_CTRL                                                                                                   | 131  |

|     | 3.3.5.11 DPLL_CTRL                                                                                                  | 131  |

|     | 3.3.5.12 AHB_CLK_CTRL                                                                                               |      |

|     | 3.3.5.13 APB1_CLK_CTRL0                                                                                             |      |

|     | 3.3.5.14 APB1 CLK CTRL1                                                                                             | 135  |

|     | 3.3.5.15 APB2 CLK CTRL0                                                                                             | 136  |

|     | 3.3.5.16 APB2 CLK CTRL1                                                                                             |      |

|     | $3.3.5.17 \text{Act}$ $3\overline{2}k \text{ctr}\overline{1}$                                                       |      |

|     | 3.3.5.18 Act 32k basecorr                                                                                           |      |

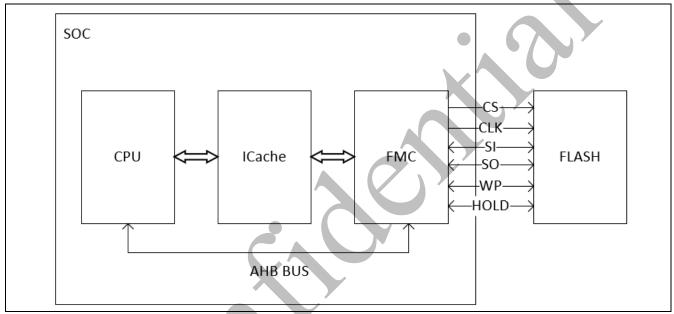

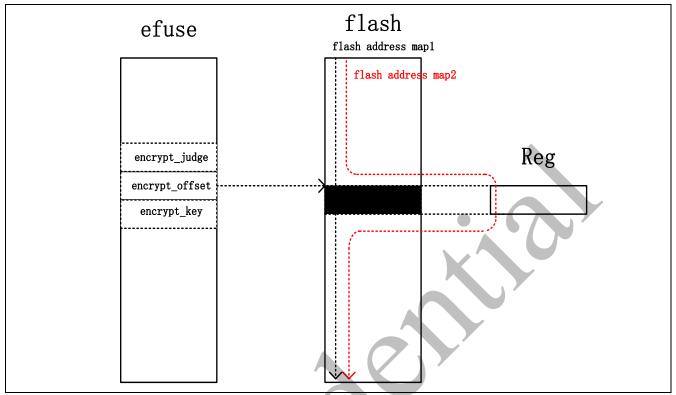

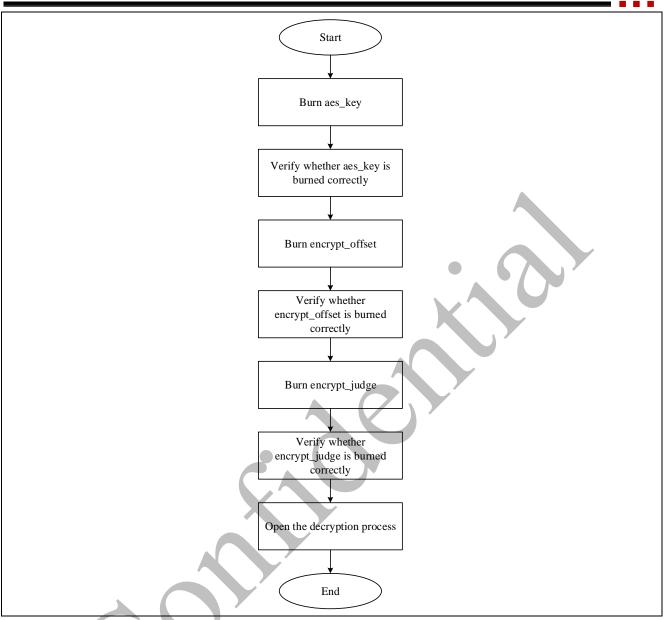

| 3.4 | Flash Memory Controller (FMC)                                                                                       |      |

| 5.1 | 3.4.1 Overview                                                                                                      |      |

|     | 3.4.2 Feature                                                                                                       |      |

|     | 3.4.3 I-cache                                                                                                       |      |

|     | 3.4.3.1 I-cache Register Map                                                                                        |      |

|     |                                                                                                                     |      |

|     | 3.4.3.2 I-cache Register description                                                                                |      |

|     | I_cache Control Register (x_cache_en )                                                                              |      |

|     | I_cache Initialize Control Register (x_cache_ini)                                                                   |      |

|     | 3.4.4 IAP                                                                                                           |      |

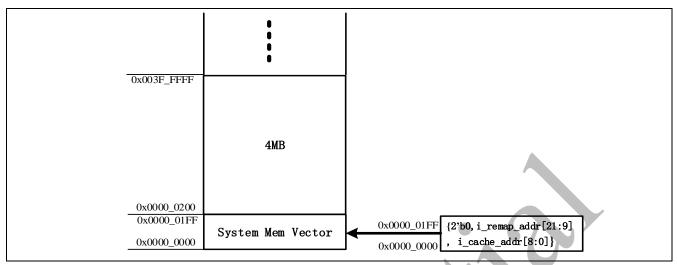

|     | 3.4.4.1 Remap Function                                                                                              |      |

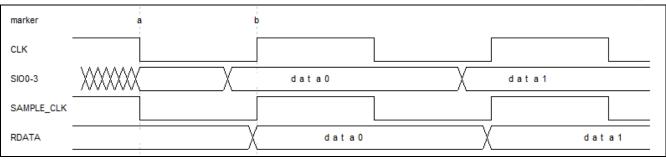

|     | 3.4.4.2 Timing Calibration                                                                                          |      |

|     | 3.4.5 SPI Flash Register Map                                                                                        |      |

|     | 3.4.6 SPI Flash Register Description                                                                                |      |

|     | 3.4.6.1 Read Data Register (X_FL_CTL)                                                                               | 145  |

|     |                                                                                                                     |      |

|     | 3.4.6.2 Trigger Register (X FL TRG)                                     | 145 |

|-----|-------------------------------------------------------------------------|-----|

|     | 3.4.6.3 Configure Register (X FL CONFIG)                                |     |

|     | 3.4.6.4 Write Data Register (X FL WDATA1)                               |     |

|     | 3.4.6.5 Write Data Register2 (X_FL_WDATA2)                              |     |

|     | 3.4.6.6 Write Data Register3 (X FL WDATA3).                             | 147 |

|     | 3.4.6.7 Write Data Register4 (X_FL_WDATA4)                              |     |

|     | 3.4.6.8 Write Data Register 5 (X FL WDATA5).                            |     |

|     | 3.4.6.9 Write Data Register6 (X FL WDATA6)                              |     |

|     | 3.4.6.10 SPI Flash Mode Select Register (X FL X MODE)                   |     |

|     | 3.4.6.11 X2 Command Select Register (X FL X2 CMD)                       |     |

|     | 3.4.6.12 X4 Command Select Register (X_FL_X4_CMD)                       |     |

|     | 34613X FL DP CMD                                                        | 149 |

|     | 3.4.6.13 X_FL_DP_CMD                                                    | 149 |

|     | 3.4.6.15 X FL REMAP ADDR                                                | 150 |

|     | 34616X FL DP CTI                                                        | 150 |

| 3.5 | 3.4.6.16 X_FL_DP_CTL                                                    | 151 |

| 5.5 | 351 Overview                                                            | 151 |

|     | 3.5.2 Feature                                                           | 151 |

|     | 3.5.2     Feature                                                       | 152 |

|     | 3.5.4     User Operation Process                                        | 152 |

|     | 3.5.5     Specific Protection Precautions.                              | 155 |

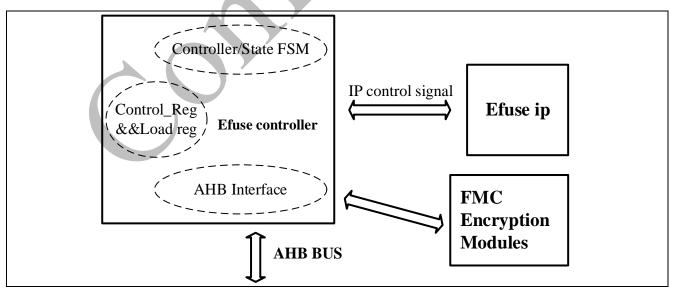

| 3.6 | eFuse Controller                                                        |     |

| 5.0 | 3.6.1 Overview                                                          | 156 |

|     | 3.6.1       Overview         3.6.2       Feature                        | 156 |

|     | 3.6.3 Block Diagram                                                     | 156 |

|     | 3.6.4 Functional Description                                            | 150 |

|     | 3.6.4.1 eFuse Introduction                                              | 157 |

|     | eFuse Feature                                                           | 157 |

|     | Fusing Requirements                                                     | 157 |

|     | 3.6.5 eFuse Controller Register Map                                     |     |

|     | 3.6.6 eFuse Controller Register Description                             |     |

|     | 3.6.6.1 EFUSE CTL                                                       |     |

|     | 3.6.6.2 EFUSE ADDR                                                      |     |

|     | 3.6.6.3 EFUSE_ADDX                                                      |     |

|     | 3.6.6.4 EFUSE VDD                                                       |     |

|     | 3.6.6.5 EFUSE_VDD                                                       |     |

|     | 3.6.6.6EFUSE_TRG                                                        |     |

|     | 3.6.6.7EFUSE PROG TIMING1                                               |     |

|     | 3.6.6.8 EFUSE PROG TIMING1                                              |     |

|     | 3.6.6.9 EFUSE_PROG_TIMING2                                              |     |

|     | 3.6.6.10EFUSE READ TIMING4                                              |     |

|     | 3.6.6.11 EFUSE_READ_TIMING5                                             |     |

|     | 3.6.6.12 EFUSE OP ERROR                                                 |     |

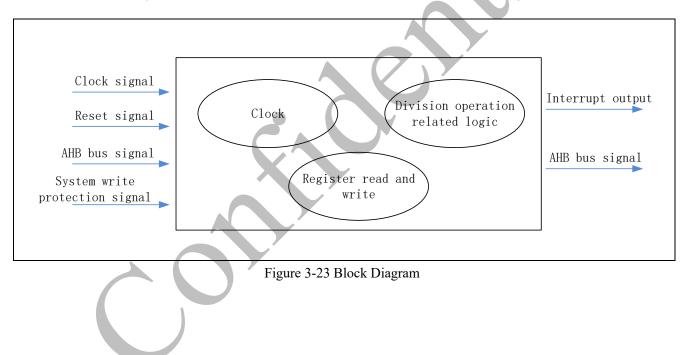

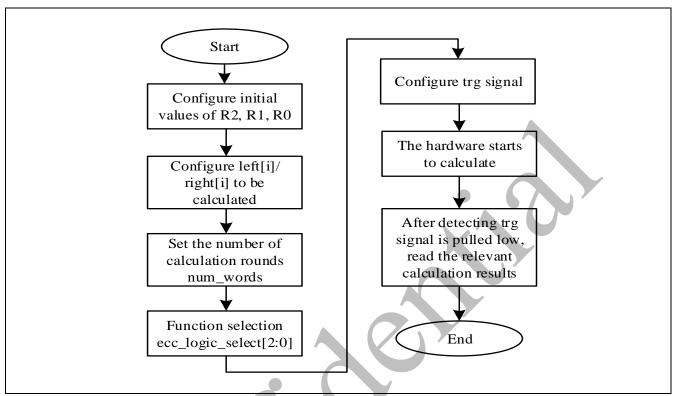

| 3.7 | ECC Accelerator                                                         |     |

| 5.7 | 3.7.1 Overview                                                          |     |

|     | 3.7.2 Features                                                          |     |

|     |                                                                         |     |

|     | <ul><li>3.7.3 Block Diagram</li></ul>                                   |     |

|     | 3.7.4     Software Process       3.7.5     ECC Accelerator Register Map |     |

|     |                                                                         |     |

|     | 3.7.6 ECC Accelerator Register Description                              |     |

|     | 3.7.6.1 ecc_r0<br>3.7.6.2 ecc_r1                                        |     |

|     | 3.7.6.2 ecc_r1                                                          |     |

|     | 3.7.6.3 ecc_r2                                                          |     |

|     | 3.7.6.4 ecc_trg                                                         |     |

|     | 3.7.6.5 ecc_irq                                                         |     |

|     | 3.7.6.6 acc_trg                                                         | 108 |

|     | 3.7.6.7 ecc logic select                                          | 168 |

|-----|-------------------------------------------------------------------|-----|

|     | 3.7.6.8 num words                                                 |     |

|     | 3.7.6.9 source a                                                  |     |

|     | 3.7.6.10 source b                                                 |     |

|     | 3.7.6.11 reg left x                                               |     |

|     | 3.7.6.12 reg right x                                              |     |

|     | 3.7.6.13 result[i]                                                |     |

|     | 3.7.6.14 mult div select                                          |     |

|     | 3.7.6.15  result 1                                                |     |

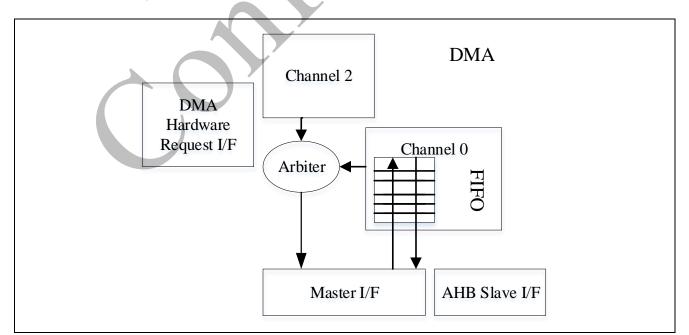

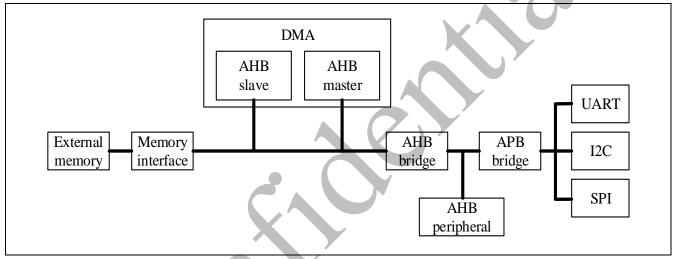

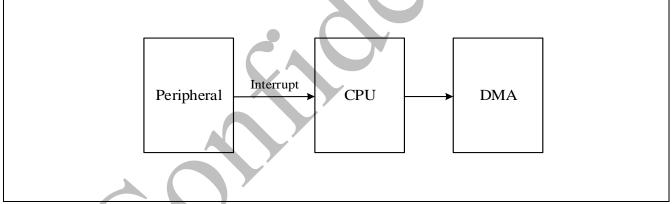

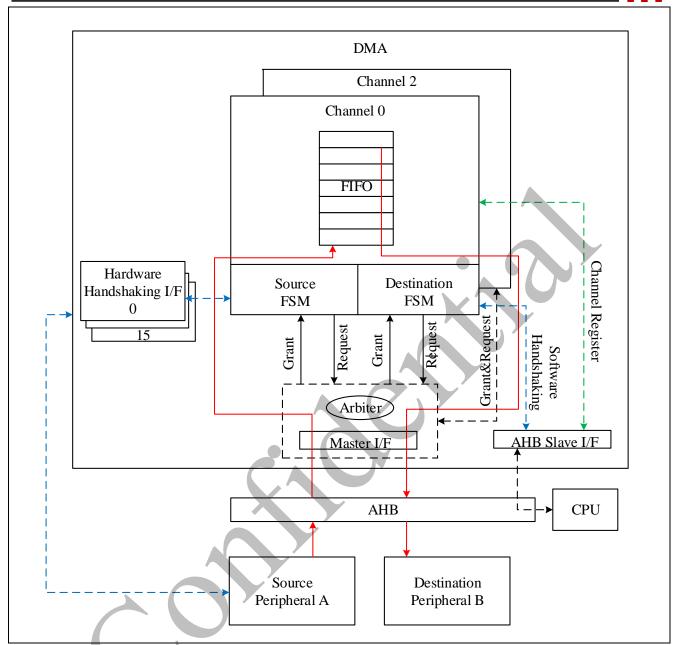

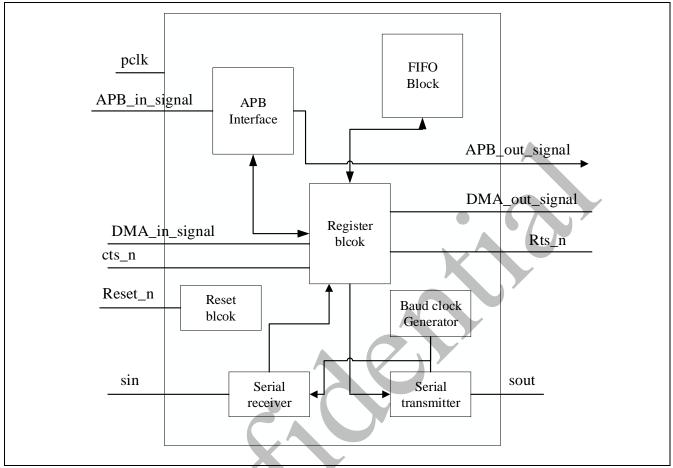

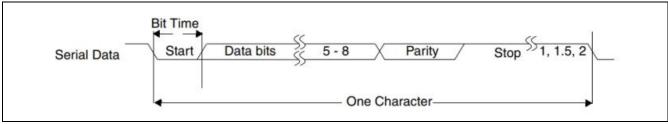

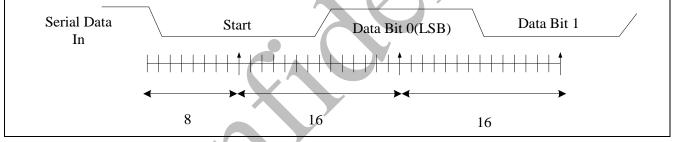

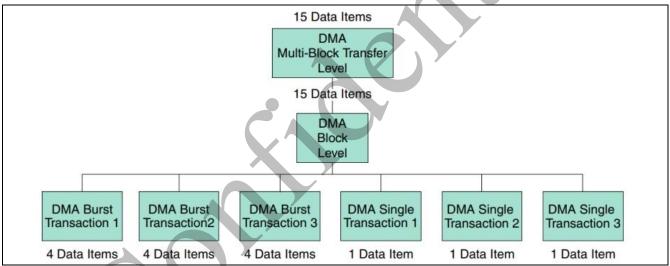

| 3.8 | DMA Serial Interface Controller (DMA)                             |     |

|     | 3.8.1 Overview                                                    |     |

|     | 3.8.2 Features                                                    |     |

|     | 3.8.3 Block Diagram                                               |     |

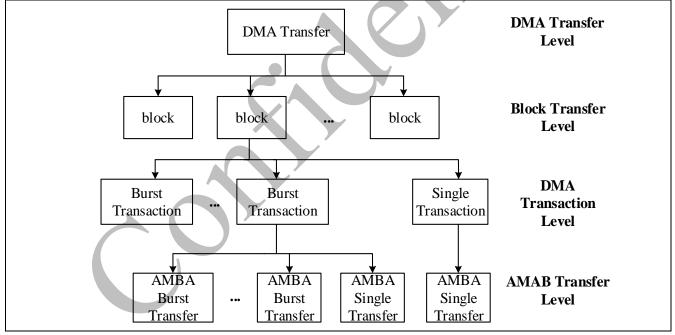

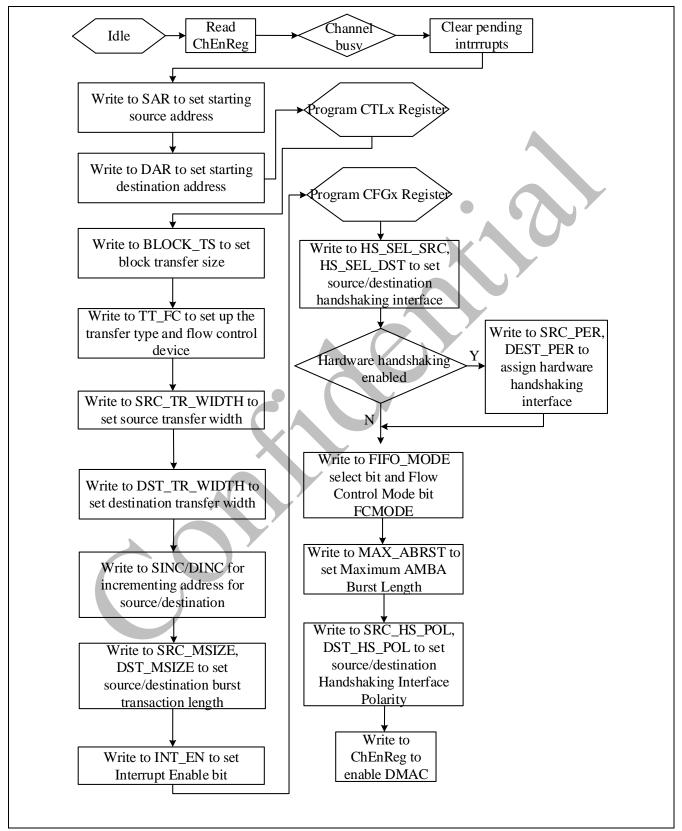

|     | 3.8.4 Functional Description                                      | 172 |

|     | 3.8.4.1 AHB master interface                                      |     |

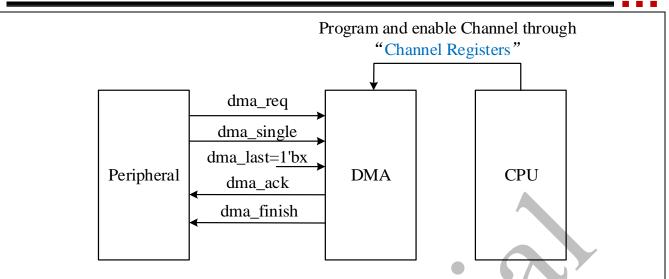

|     | 3.8.4.2 Handshaking Interface                                     |     |

|     | 3.8.4.3 Block Flow Controller and Transfer Type                   | 174 |

|     | 3.8.4.4 Basic Interface Definitions                               | 175 |

|     | 3.8.4.5 Single-block Transfer                                     | 176 |

|     | 3.8.4.6 Peripheral Burst Transaction Requests                     | 179 |

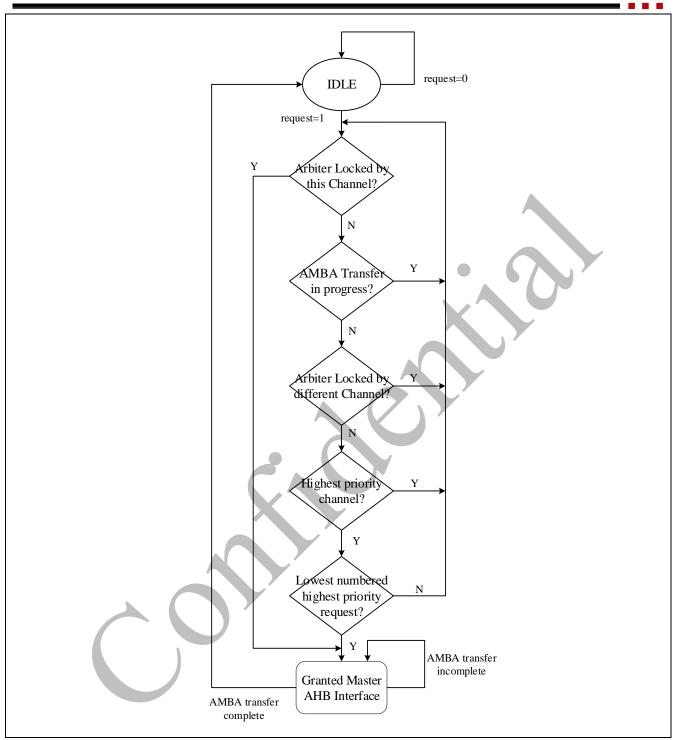

|     | 3.8.4.7 Generating Requests for the AHB Master Bus Interface      | 179 |

|     | 3.8.4.8 Interrupt                                                 | 181 |

|     | 3.8.4.8 Interrupt<br>3.8.4.9 Arbitration for AHB Master Interface | 182 |

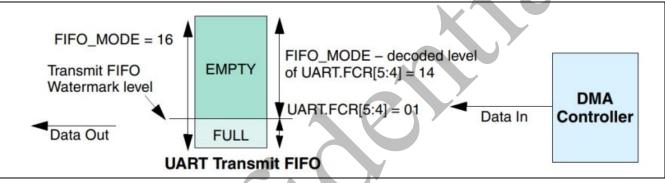

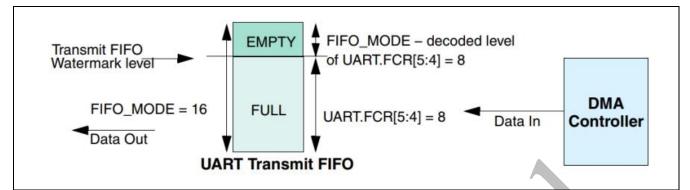

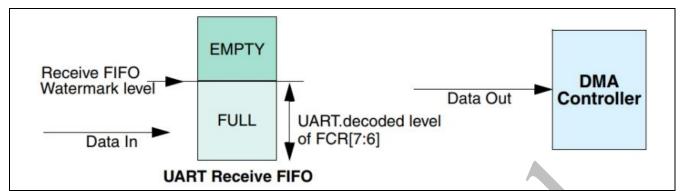

|     | 3.8.4.10 IP DMA Control                                           | 184 |

|     | 3.8.5 DMA Register Man                                            | 184 |

|     | 3.8.6 DMA Register Description                                    | 186 |

|     | 3.8.6.1 Configuration and Channel Enable Register                 | 186 |

|     | DMA Configuration Register (DmaCfgReg)                            |     |

|     | DMA Channel Enable Register (ChEnReg)                             |     |

|     | 3.8.6.2 Channel Register                                          |     |

|     | Source Address Register for Channel x Register (SARx)             |     |

|     | Destination Address Register for Channel x(DARx)                  |     |

|     | Control Register for Channel x(CTLx)                              |     |

|     | Configuration Register for Channel x(CFGx)                        |     |

|     | 3.8.6.3 Interrupt Registers.                                      |     |

|     | Interrupt Raw Status Registers (IRSR)                             |     |

|     | Interrupt Status Registers(ISR)                                   |     |

|     | Interrupt Mask Registers (IMR)                                    |     |

|     | Interrupt Clear Registers (ICR)                                   |     |

|     | Combined Interrupt Status Register (Statusint)                    |     |

|     | 3.8.6.4 Software Handshaking Registers                            |     |

|     | Source Software Transaction Request Register (ReqSrcReg)          |     |

|     | Destination Software Transaction Request Register (ReqDstReg)     |     |

|     | Single Source Transaction Request Register (SglReqSrcReg)         |     |

|     | Single Destination Transaction Request Register (SglReqDstReg)    |     |

|     | Last Source Transaction Request Register(LstSrcReg)               |     |

|     | Last Destination Transaction Request Register(LstDstReg)          |     |

|     | 3.8.6.5 Miscellaneous DMA Registers.                              |     |

|     | DMA ID Register (DmaIdReg)                                        |     |

|     | DMA Test Register (DmaTestReg)                                    |     |

|     | DMA Component Parameters Register 3(DMA COMP PARAMS 3)            |     |

|     | DMA Component Parameters Register 2(DMA COMP PARAMS 2)            |     |

|     | DMA Component Parameters Register 1(DMA COMP PARAMS 1)            |     |

|     | DMA Component ID Register (DCIR).                                 |     |

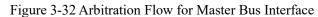

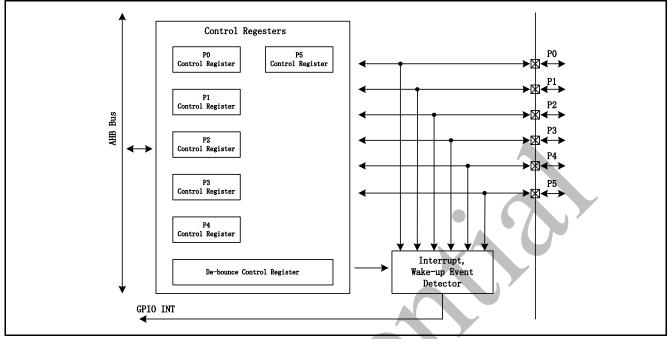

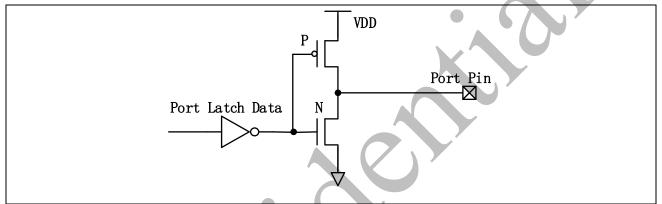

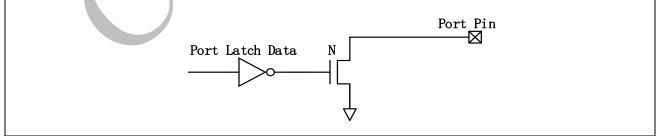

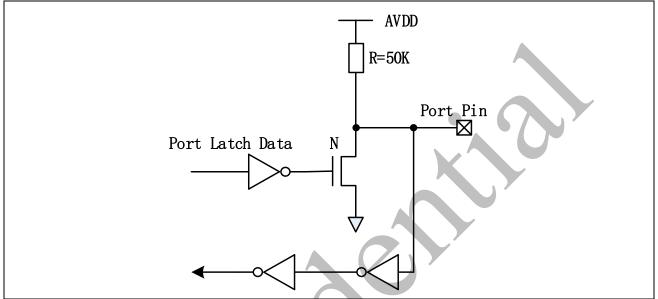

| 3.9 | General Purpose I/O (GPIO).                                       |     |

| /   | 3.9.1 Overview                                                    |     |

|     |                                                                   |     |

|      | 3.9.2   | Features                                                                     | 208  |

|------|---------|------------------------------------------------------------------------------|------|

|      | 3.9.3   | Block Diagram                                                                | 209  |

|      | 3.9.4   | Basic Configuration                                                          | 209  |

|      | 3.9.5   | Functional Description                                                       | 209  |

|      |         | .1 Input Mode                                                                |      |

|      |         | .2 Push-pull Output Mode                                                     |      |

|      |         | .3 Open-drain Output Mode                                                    |      |

|      |         | .4 Quasi-bidirectional Mode                                                  |      |

|      | 3.9.6   | GPIO Interrupt and Wake-up Function                                          |      |

|      | 3.9.7   | GPIO Register Map                                                            |      |

|      | 3.9.8   | GPIO Register Description                                                    |      |

|      | 3.9.8   | .1 Port 0-5 I/O Mode Control (Px_MODE)                                       | 215  |

|      | 3.9.8   | .2 Port 0-5 Digital Input Path Disable Control (Px_DINOFF)                   | 216  |

|      | 398     | 3 Port 0-5 Data Output Value (Px_DOUT)                                       | 217  |

|      | 3.9.8   | .4 Port 0-5 Data Output Write Mask (Px_DATMSK)                               | 218  |

|      | 3.9.8   | .5 Port 0-5 Pin Value (Px_PIN)                                               | 219  |

|      | 3.9.8   | .6 Port 0-5 De-bounce Enable Control (Px DBEN)                               | 220  |

|      | 3.9.8   | .7 Port 0-5 Interrupt Mode Control (Px_INTTYPE)                              | 221  |

|      | 3.9.8   | .8 Port 0-5 Interrupt Enable Control (Px_INTEN)                              | 222  |

|      | 3.9.8   | .9 Port 0-5 Interrupt Source Flag (Px_INTSRC)                                | 223  |

|      | 3.9.8   | .10 Interrupt De-bounce Cycle Control (GPIO DBCTL)                           | 224  |

|      | 3.9.8   | .11 GPIO Px.n Data Input/Output (Pxn_PDIO)                                   | 225  |

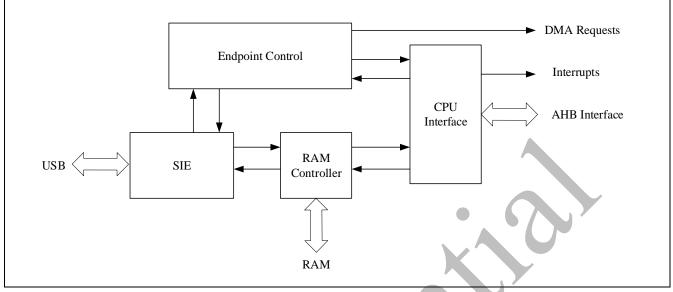

| 3.10 | Univers | .11 GPIO Px.n Data Input/Output (Pxn_PDIO)<br>al Serial Bus(USB)<br>Overview | .227 |

|      | 3.10.1  | Overview                                                                     | 227  |

|      | 3.10.2  | Features                                                                     | 227  |

|      | 3.10.3  | Block Diagram                                                                |      |

|      | 3.10.4  | Functional Description                                                       | 228  |

|      | 3.10.   | 4.1 Support BULK/ISOCHRONOUS transactions                                    | 228  |

|      | 3.10.   | 4.2 USB DMA Operation                                                        | 228  |

|      |         | DMA MODE0 : OUT/RX ENDPOINTS                                                 |      |

|      |         | DMA MODE0 : IN/TX ENDPOINTS                                                  |      |

|      |         | DMA MODE 1 : OUT/RX ENDPOINTS                                                |      |

|      |         | DMA MODE1 : IN/TX ENDPOINTS                                                  |      |

|      | 3.10.   | 4.3 Support plug in/out interrupt                                            |      |

|      | 3.10.5  | USB Register Map                                                             |      |

|      | 3.10.6  | USB Register Description                                                     |      |

|      |         | 6.1 FADDR                                                                    |      |

|      |         | 6.2 Power                                                                    |      |

|      | 3.10.   | 6.3 IntrIn1                                                                  | 235  |

|      | 3.10.   | 6.4 IntrIn2                                                                  | 235  |

|      | 3.10.   | 6.5 IntrOut1                                                                 | 235  |

|      | 3.10.   | 6.6 IntrOut2                                                                 | 236  |

|      | 3.10.   | 6.7 IntrUSB                                                                  | 236  |

|      | 3.10.   | 6.8 IntrIn1E                                                                 | 236  |

|      | 3.10.   | 6.9 IntrIn2E                                                                 | 237  |

|      | 3.10.   | 6.10 IntrOut1E                                                               | 237  |

|      | 3.10.   | 6.11 IntrOut2E                                                               | 237  |

|      | 3.10.   | 6.12 IntrUSBE                                                                | 238  |

|      | 3.10.   | 6.13 Frame1                                                                  | 238  |

|      | 3.10.   | 6.14 Frame2                                                                  | 238  |

|      | 3.10.   | 6.15 Index                                                                   | 239  |

|      | 3.10.   | 6.16 InMaxP                                                                  | 239  |

|      | 3.10.   | 6.17 CSR0                                                                    | 240  |

|      | 3.10.   | 6.18 Count0                                                                  | 240  |

|      |         | 6.19INCSR1                                                                   |      |

|      | 3.10.   | 6.20 INCSR2                                                                  | 242  |

|      |         |                                                                              |      |

|      | 3 10   | .6.21 OUTMAXP                                                                                                           | 242 |

|------|--------|-------------------------------------------------------------------------------------------------------------------------|-----|

|      |        | .6.22 OUTCSR1                                                                                                           |     |

|      |        |                                                                                                                         |     |

|      |        | .6.23 OUTCSR2                                                                                                           |     |

|      |        | .6.24 OUTCOUNT1                                                                                                         |     |

|      |        | .6.25 OUTCOUNT2                                                                                                         |     |

|      |        | .6.26 FIFOx                                                                                                             |     |

|      | 3.10   | .6.27 INTR                                                                                                              | 245 |

|      | 3.10   | .6.28 CNTL1                                                                                                             | 246 |

|      | 3.10   | .6.29 ADDR1                                                                                                             | 246 |

|      | 3.10   | .6.30 COUNT1                                                                                                            | 246 |

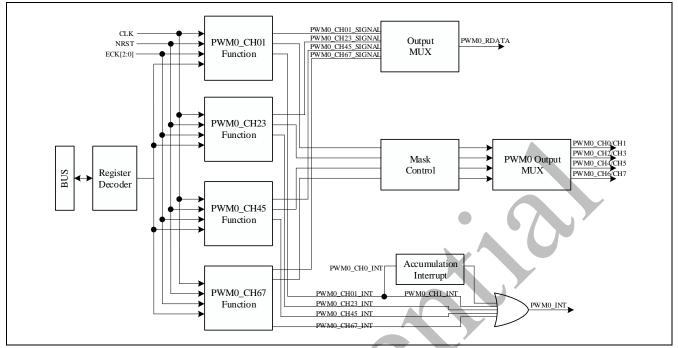

| 3.11 |        | ed PWM Generator (PWM)                                                                                                  |     |

|      | 3.11.1 | Overview                                                                                                                |     |

|      | 3.11.2 | Features                                                                                                                |     |

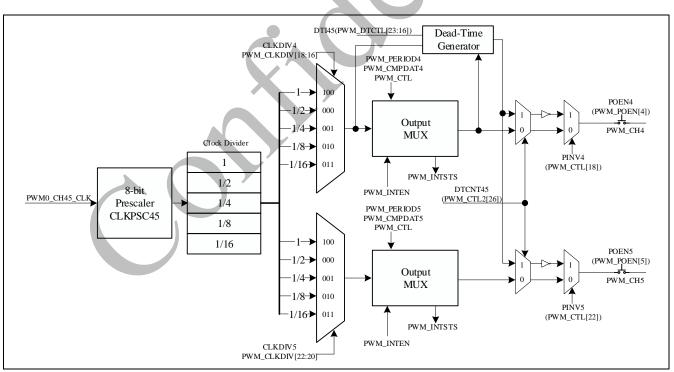

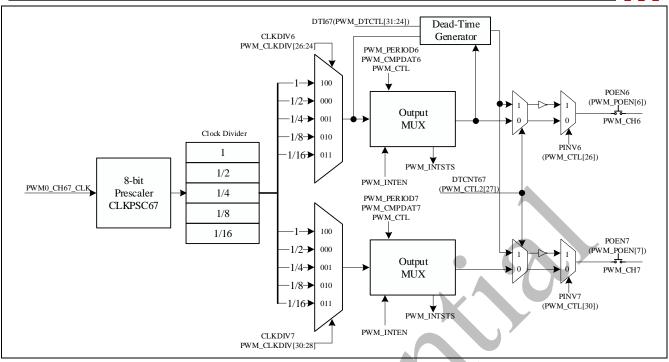

|      | 3.11.2 | Block Diagram                                                                                                           |     |

|      |        |                                                                                                                         |     |

|      | 3.11.4 | Basic Configuration                                                                                                     |     |

|      | 3.11.5 | Functional Description                                                                                                  |     |

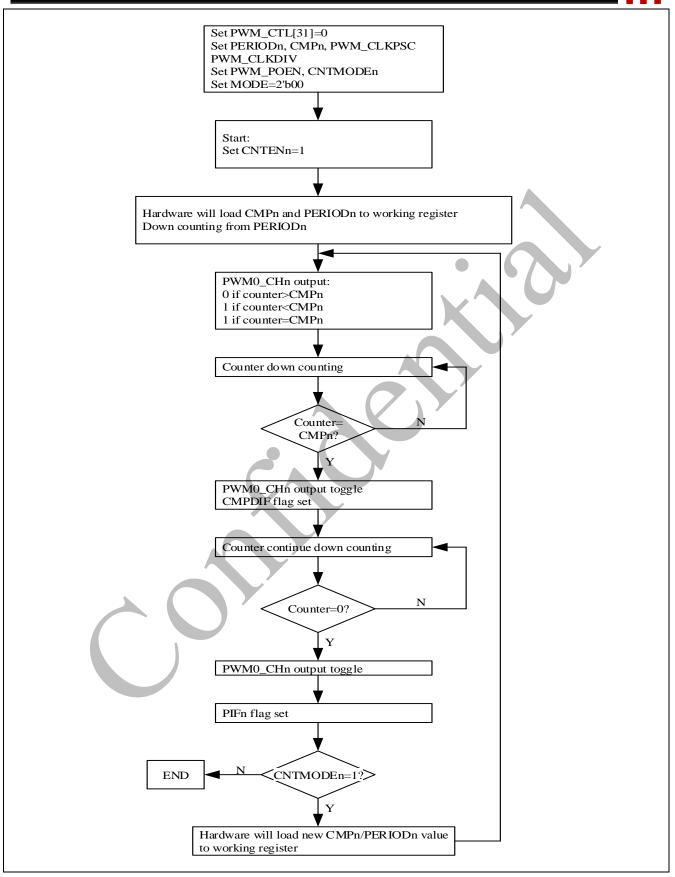

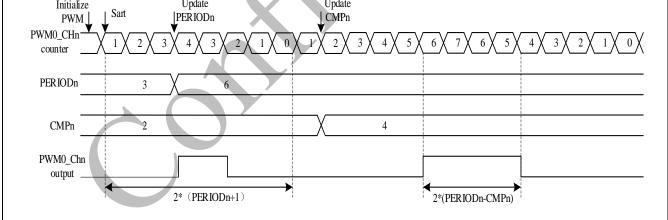

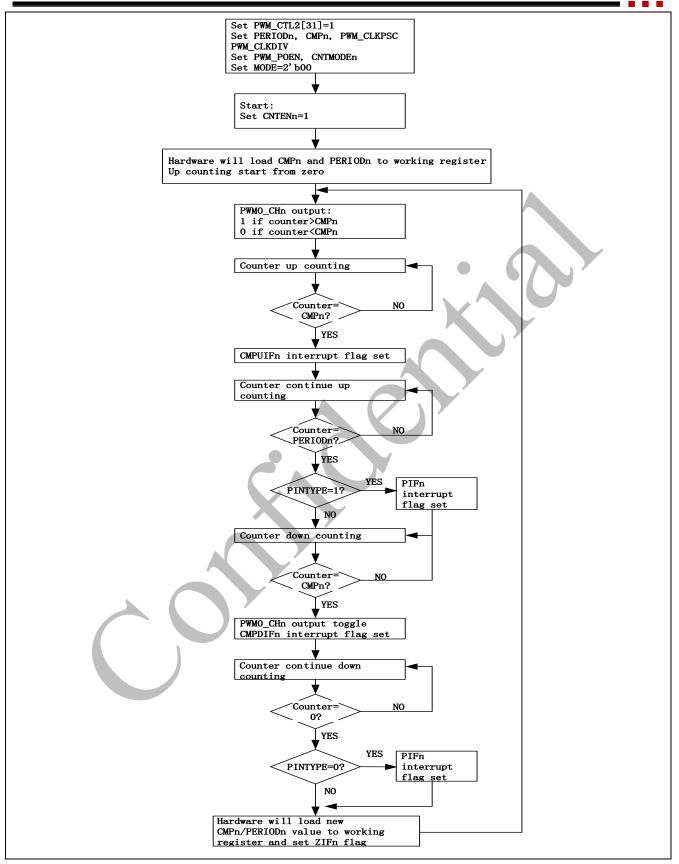

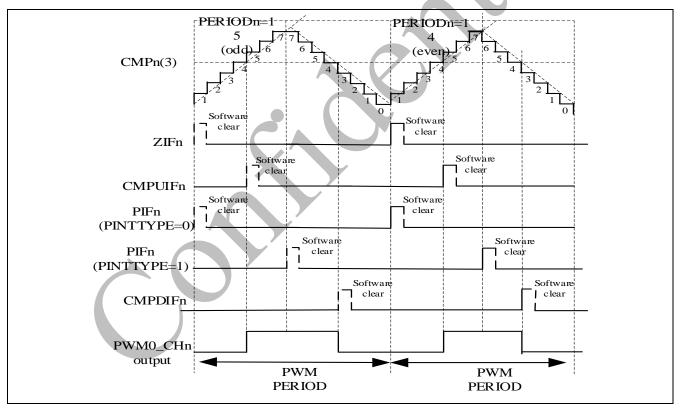

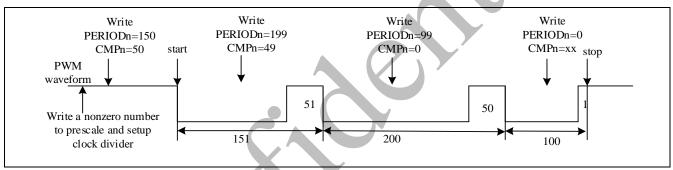

|      | 3.11   | .5.1 PWM Counter Type                                                                                                   | 252 |

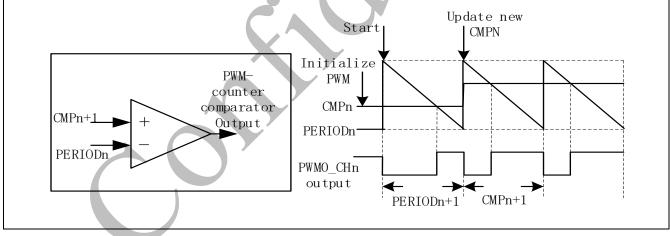

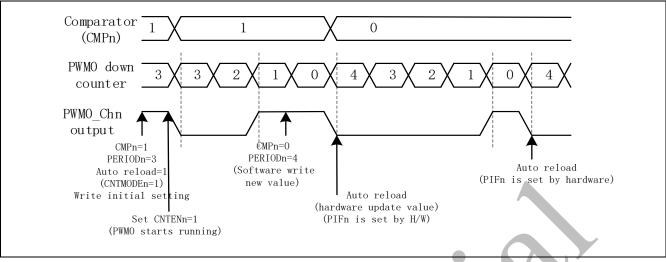

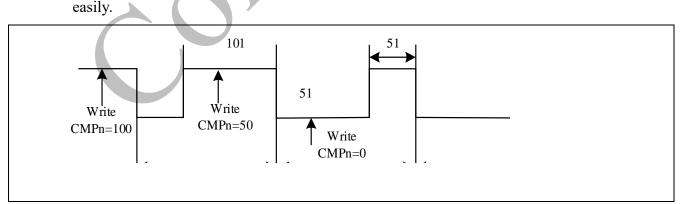

|      |        | Edge-aligned PWM (Down-counter)<br>Center-Aligned PWM (Up/Down counter)<br>Precise Center-Aligned PWM (Up/Down Counter) | 253 |

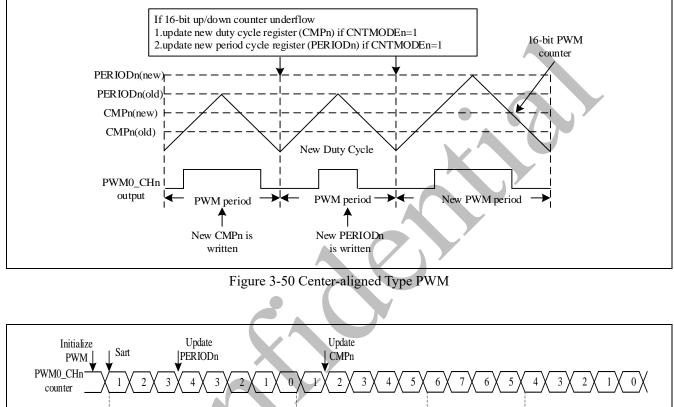

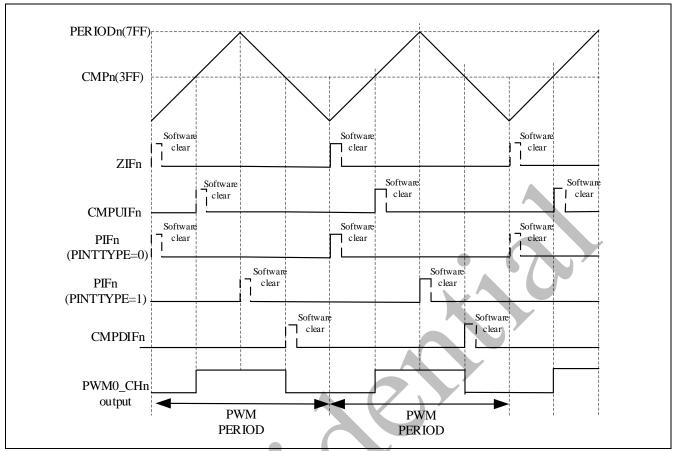

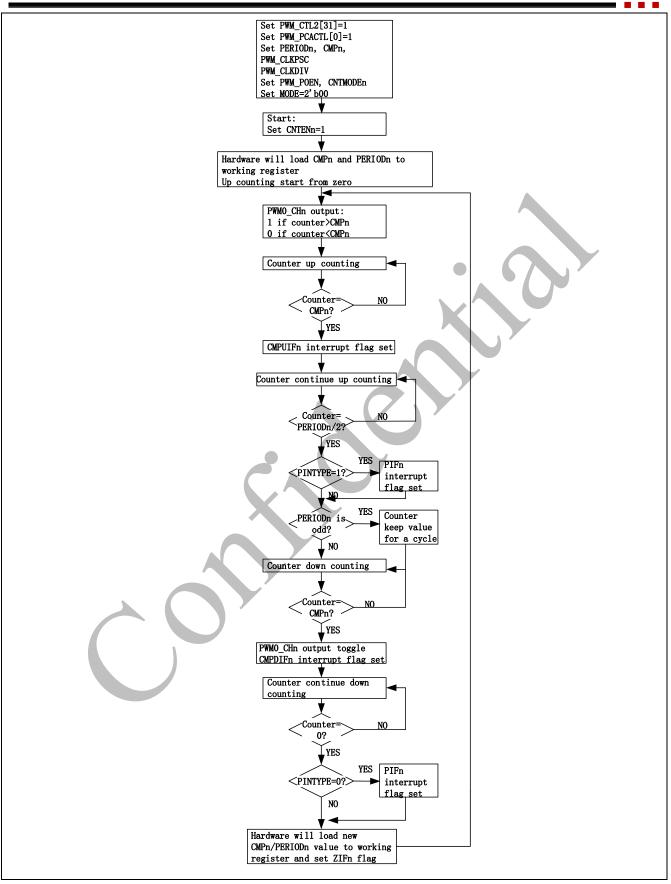

|      |        | Center-Aligned PWM (Up/Down counter)                                                                                    | 257 |

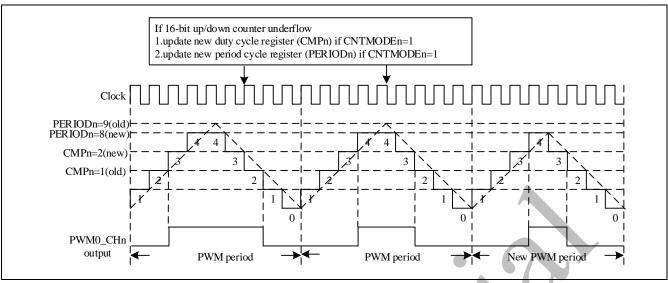

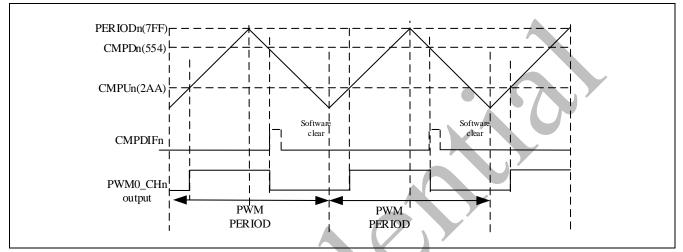

|      |        | Precise Center-Aligned PWM (Up/Down Counter)                                                                            | 261 |

|      |        | Asymmetric Mode                                                                                                         | 264 |

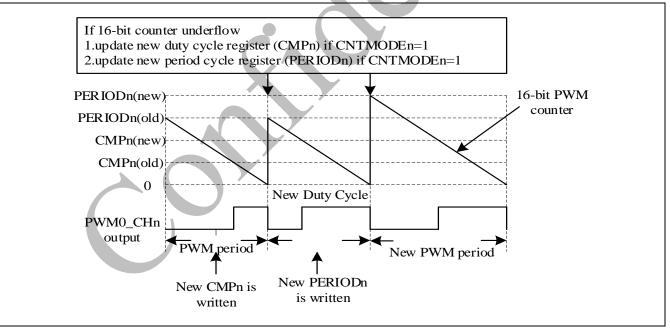

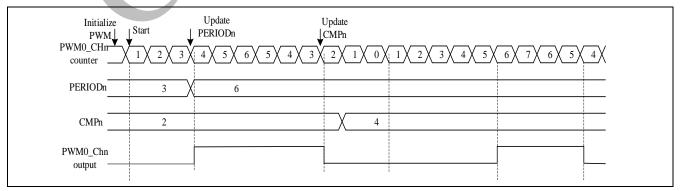

|      | 3.11   | 5.2 PWM Center Loading Operation                                                                                        | 264 |

|      | 3 11   | 5.3 PWM Double Buffering and Auto-reload Operation                                                                      | 265 |

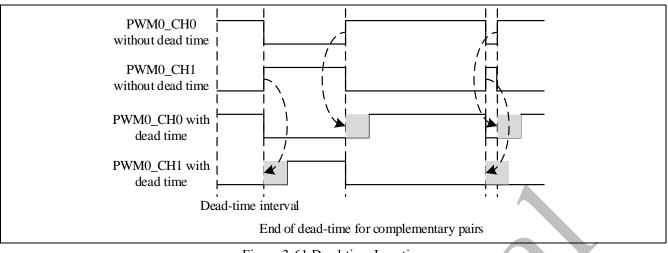

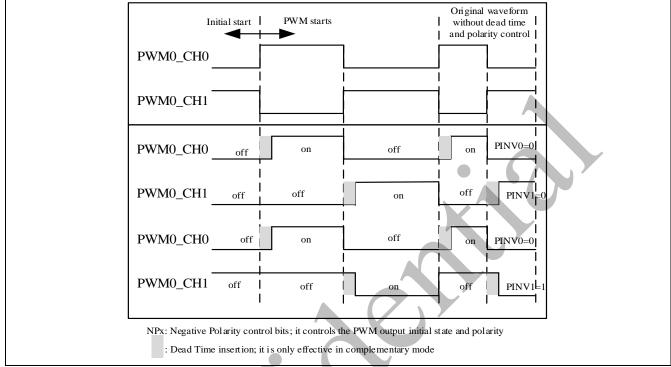

|      | 3 11   | 5.4 PWM Operation Modes                                                                                                 | 205 |

|      | 5.11   | 5.4 PWM Operation Modes                                                                                                 | 200 |

|      |        |                                                                                                                         | 200 |

|      |        | Complementary Mode<br>Synchronous Mode                                                                                  | 200 |

|      |        | Synchronous Mode                                                                                                        | 267 |

|      |        | Group Mode                                                                                                              | 267 |

|      | 3.11   | 5.5 Polarity Control                                                                                                    | 267 |

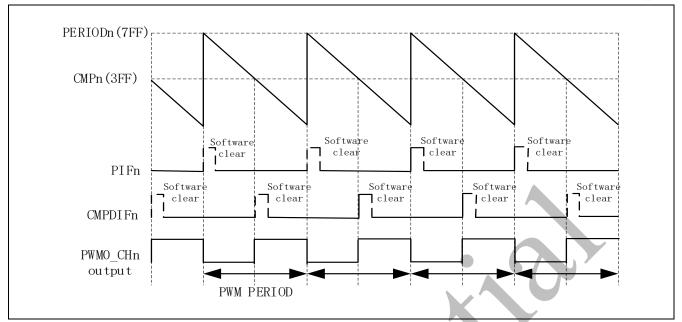

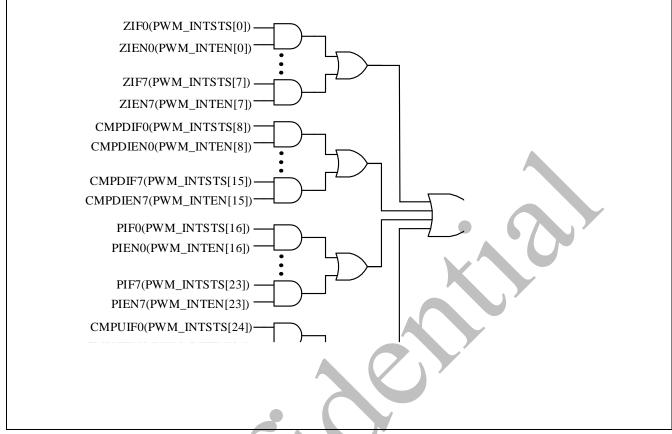

|      | 3.11   | .5.6 PWM Interrupt Architecture                                                                                         | 268 |

|      | 3.11.6 | PWM Control Register Map                                                                                                | 270 |

|      | 3.11.7 | PWM Control Register Description                                                                                        |     |

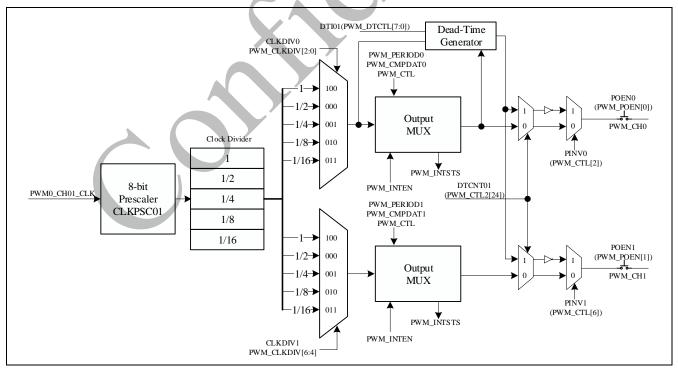

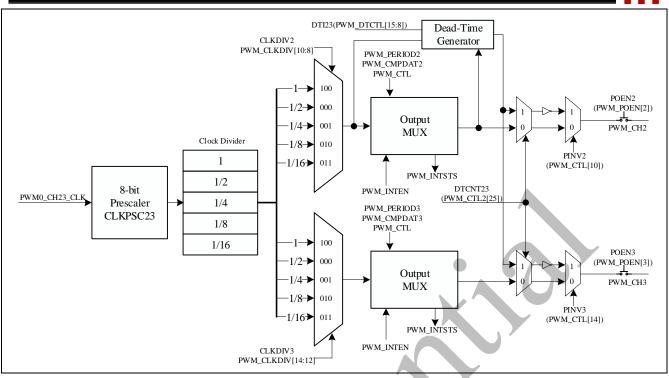

|      | 3.11   | 7.1 PWM Pre-Scale Register (PWM CLKPSC)                                                                                 |     |

|      | 3 11   | 7.2 PWM Clock Selector Register (PWM_CLKDIV)                                                                            | 272 |

|      | 3 11   | 7.3 PWM Control Register (PWM CTL)                                                                                      | 274 |

|      |        | 7.4 PWM Counter Register 0-7 (PWM_PERIOD0-7)                                                                            |     |

|      |        | 7.5 PWM Comparator Register 0-7 (PWM CMPDAT0-7)                                                                         |     |

|      |        |                                                                                                                         |     |

|      |        | 7.6 PWM Control Register2 (PWM_CTL2)                                                                                    |     |

|      |        | 7.7 PWM Flag Indication Register (PWM_FLAG)                                                                             |     |

|      |        | 7.8 PWM Interrupt Enable Register (PWM_INTEN)                                                                           |     |

|      |        | .7.9 PWM Interrupt Indication Register (PWM_INTSTS)                                                                     |     |

|      | 3.11   | 7.10 PWM Output Control Register (PWM_POEN)                                                                             | 281 |

|      | 3.11   | 7.11 PWM Dead-time Interval Register (PWM DTCTL)                                                                        | 282 |

|      | 3.11   | 7.12 PWM Trigger ADC Control Register (PWM ADCTCTL0)                                                                    | 283 |

|      |        | .7.13 PWM Trigger ADC Control Register (PWM ADCTCTL1)                                                                   |     |

|      |        | 7.14 PWM Trigger Status Register (PWM ADCTSTS0)                                                                         |     |

|      |        | .7.15 PWM Trigger Status Register (PWM ADCTSTS1)                                                                        |     |

|      |        | .7.16 Precise PWM Center-Aligned Type Control Register (PWM PCACTL)                                                     |     |

|      |        |                                                                                                                         |     |

|      | 3.11.8 | Operation Steps                                                                                                         |     |

|      |        | 8.1 PWM Counter Start Procedure                                                                                         |     |

|      |        | 8.2 PWM Counter Stop Procedure                                                                                          |     |

| 3.12 |        | og Timer (WDT)                                                                                                          |     |

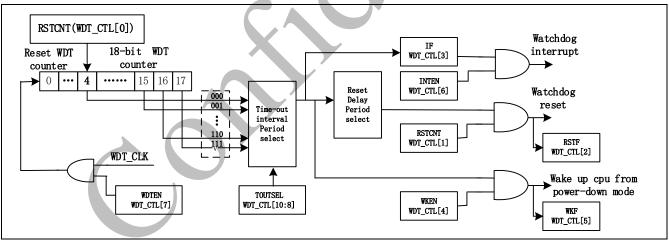

|      | 3.12.1 | Overview                                                                                                                |     |

|      | 3.12.2 | Features                                                                                                                | 295 |

|      | 3.12.3 | Block Diagram                                                                                                           | 295 |

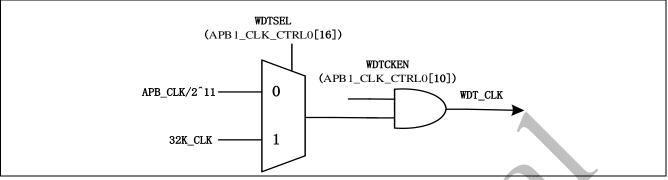

|      | 3.12.4 | Clock Control                                                                                                           |     |

|      |        |                                                                                                                         |     |

|       | 3.12.5       | Basic Configuration                                            | 296 |

|-------|--------------|----------------------------------------------------------------|-----|

|       | 3.12.6       | Functional Description                                         |     |

|       | 3.12         | 2.6.1 WDT Time-out Flag                                        |     |

|       |              | 2.6.2 WDT Time-out Interrupt Flag                              |     |

|       |              | 2.6.3 WDT Reset Delay Period and Reset System                  |     |

|       |              | 2.6.4 WDT Wake-up                                              |     |

|       | 3.12.7       | WDT Control Register Map                                       |     |

|       | 3.12.8       | WDT Register Description                                       |     |

|       | 3.12         | 2.8.1 WDT Control Register (WDT CTL)                           |     |

|       |              | 2.8.2 WDT Alternative Control Register (WDT ALTCTL)            |     |

| 3.13  |              | w Watchdog Timer (WWDT)                                        |     |

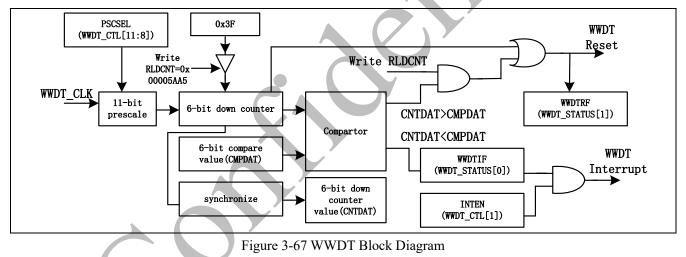

|       | 3.13.1       | Overview                                                       |     |

|       | 3.13.2       | Feature                                                        |     |

|       | 3.13.3       | Block Diagram                                                  |     |

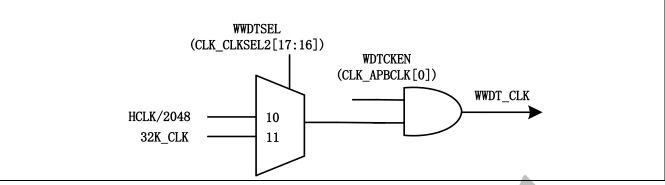

|       | 3.13.4       | Clock Control                                                  |     |

|       | 3.13.5       | Functional Description                                         |     |

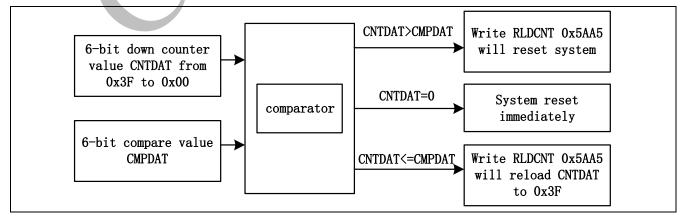

|       | 3.13         | 3.5.1 WWDT Counting                                            |     |

|       | 3.13         | 3.5.2 WWDT Compare Match Flag                                  | 304 |

|       | 3.13         | <ul> <li>3.5.2 WWDT Compare Match Flag</li></ul>               | 304 |

|       | 3 1 3        | 5 5 4 WWDT Reset System                                        | 304 |

|       | 3 1 3        | 5 5 WWDT Window Setting Limitation                             | 305 |

|       | 3.13.6       | WWDT Control Register Man                                      | 306 |

|       | 3.13.7       | WWDT Control Register Map<br>WWDT Register Description         | 306 |

|       |              | 8.7.1 WWDT Reload Counter Register (WWDT_RLDCNT)               | 300 |

|       | 2.12         | 8.7.2 WWDT Control Register (WWDT_CTL)                         | 300 |

|       | 5.15<br>2.12 | 2.7.2 WWDT Status Devistor (WWDT STATUS)                       | 507 |

|       | 3.13         | 3.7.3 WWDT Status Register (WWDT_STATUS)                       | 308 |

| 2 1 4 | 3.13         | 3.7.4 WWDT Counter Value Register (WWDT_CNT)                   | 308 |

| 3.14  |              | rial Interface Controller (I2C)                                |     |

|       | 3.14.1       | Overview                                                       |     |

|       | 3.14.2       | Features                                                       |     |

|       | 3.14.3       | Block Diagram                                                  |     |

|       | 3.14.4       | Functional Description                                         |     |

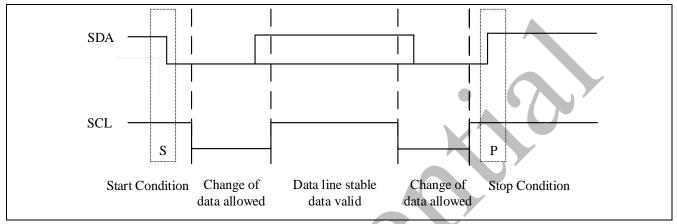

|       |              | 4.1 I2C Behavior                                               |     |

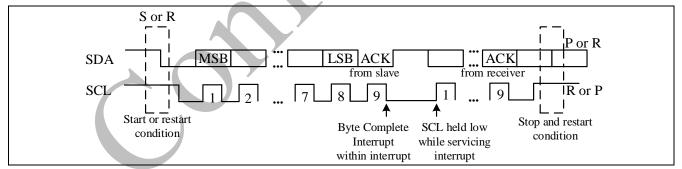

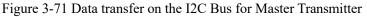

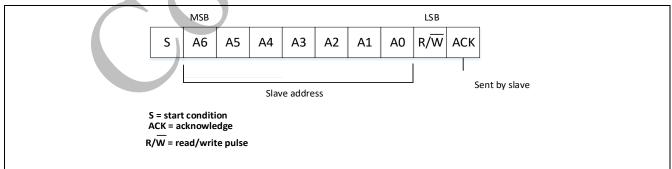

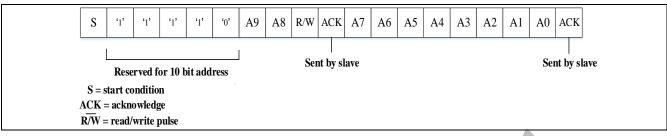

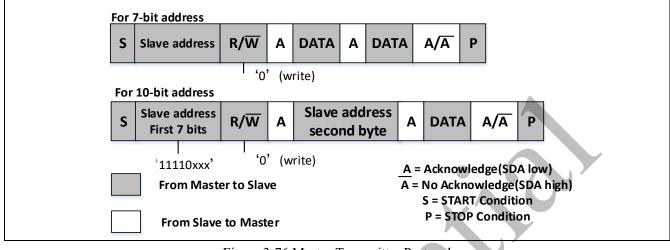

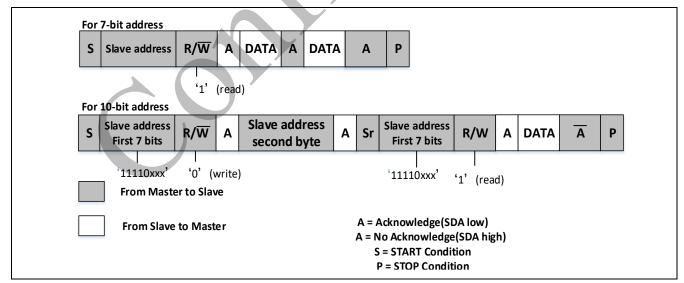

|       | 3.14         | 4.4.2 I2C Protocols                                            |     |

|       |              | START and STOP Conditions                                      |     |

|       |              | Addressing Slave Protocol                                      |     |

|       |              | Transmitting and Receiving Protocol                            |     |

|       | 3.14         | .4.3 Tx FIFO Management and START, STOP and RESTART Generation | 316 |

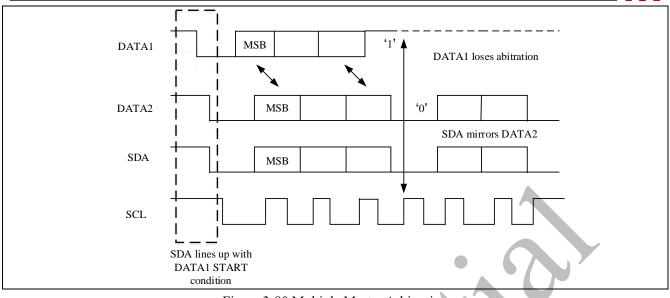

|       | 3.14         | .4.4 Multiple Master Arbitration                               | 317 |

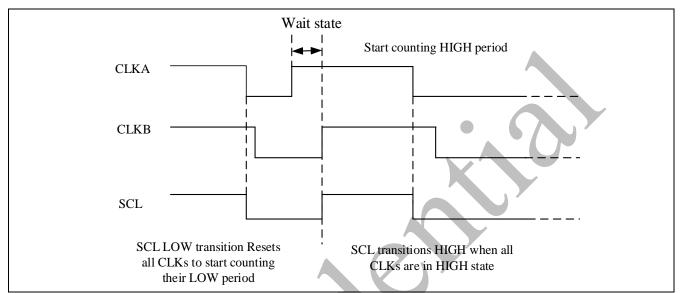

|       | 3.14         | 1.4.5 Clock Synchronization                                    | 318 |

|       | 3.14         | 1.4.6 Operation Modes                                          | 319 |

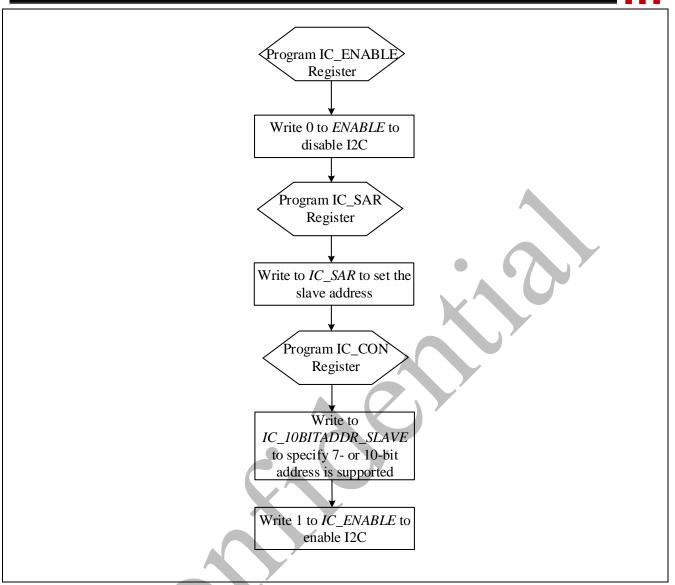

|       |              | Slave Mode Operation                                           | 319 |

|       |              | Master Mode Operation                                          |     |

|       |              | Disabling I2C                                                  |     |

|       |              | Aborting I2C Transfers                                         |     |

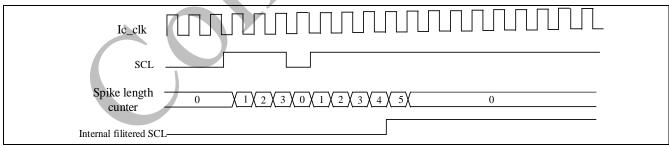

|       | 3.14         | I.4.7 Spike Suppression                                        |     |

|       |              | 4.4.8 Fast Mode Plus Operation                                 |     |

|       |              | 4.9 IC CLK Frequency Configuration                             |     |

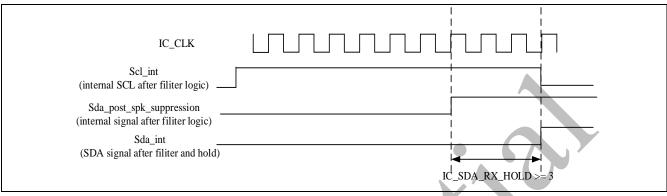

|       |              | 4.4.10 SDA Hold Time                                           |     |

|       | 5.1          | SDA Hold Timings in Receiver                                   |     |

|       |              | SDA Hold Timings in Transmitter                                |     |

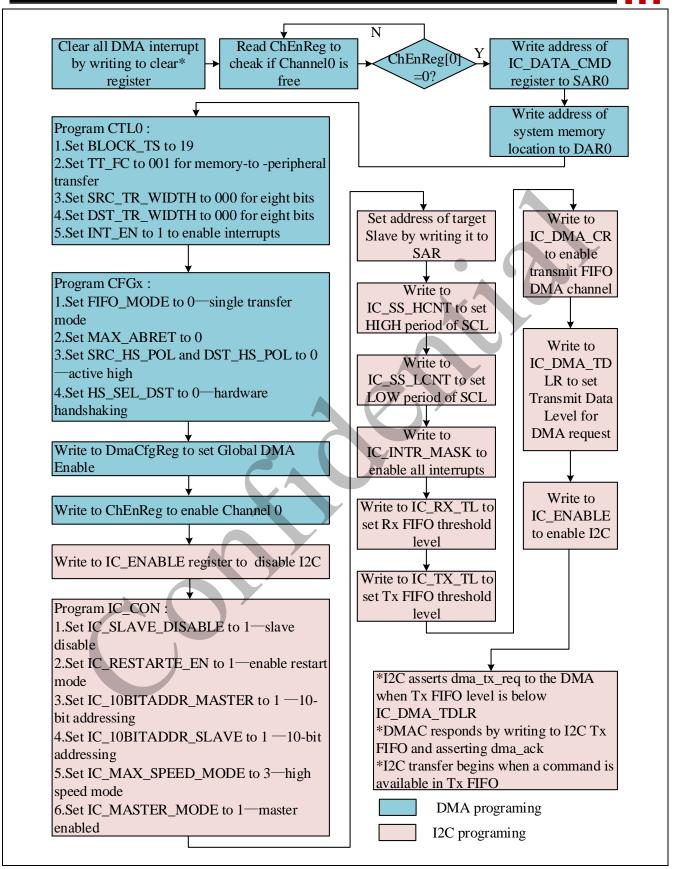

|       | 21/          | 4.4.11 DMA Controller Interface                                |     |

|       | 3.14.5       | I2C Register Map                                               |     |

|       |              |                                                                |     |

|       | 3.14.6       | Operation of Interrupt Registers                               |     |

|       | 3.14.7       | I2C Register Description                                       |     |

|       | 3.14         | k.7.1 IC_CON                                                   | 335 |

| 3.1/         | 4.7.2 IC TAR                                                                                   | 337        |

|--------------|------------------------------------------------------------------------------------------------|------------|

|              | 1.7.3 IC_SAR                                                                                   |            |

|              |                                                                                                |            |

|              | 4.7.4 IC_HS_MADDR                                                                              |            |

|              | 4.7.5 IC_DATA_CMD                                                                              |            |

|              | 4.7.61C_SS_SCL_HCNT                                                                            |            |

|              | 1.7.7 IC_SS_SCL_LCNT                                                                           |            |

|              | A.7.8 IC_FS_SCL_HCNT                                                                           |            |

|              | 1.7.9 IC_FS_SCL_LCNT                                                                           |            |

|              | A.7.10 IC_HS_SCL_HCNT                                                                          |            |

|              | A.7.11 IC_HS_SCL_LCNT                                                                          |            |

| 3.14         | 1.7.12 IC INTR STAT                                                                            | 343        |

| 3.14         | 4.7.13 IC_INTR_MASK<br>4.7.14 IC_RAW_INTR_STAT                                                 | 343        |

| 3.14         | 7.14 IC RAW INTR STAT                                                                          | 344        |

| 3.14         | 4.7.15 IC RX TL                                                                                | 346        |

|              | 4.7.16IC_TX_TL                                                                                 |            |

| 3.1          | 4.7.17 IC_CLR_INTR                                                                             | 346        |

| 3.14         | A.7.18IC CLR RX UNDER                                                                          | 340<br>347 |

| 3.14<br>2.14 | 17 10 IC_CLD_DV_OVED                                                                           | 347        |

| 5.14         | A 7 201C CLR KA UVER                                                                           | 547        |

| 3.14         | 4.7.19 IC_CLR_RX_OVER<br>4.7.20 IC_CLR_TX_OVER<br>4.7.21 IC_CLR_RD_REQ<br>4.7.21 IC_CLR_RD_REQ | 347        |

| 3.14         | F. 7.21 IC_CLR_RD_REQ                                                                          | 347        |

| 3.14         | F. / .22 IC_CLR_IX_ABKI                                                                        | 348        |

| 3.14         | A.7.23 IC_CLR_RX_DONE                                                                          | 348        |

| 3.14         | H.7.24 IC_CLR_ACTIVITY                                                                         | 348        |

| 3.14         | 4.7.25 IC_CLR_STOP_DET                                                                         | 349        |

| 3.14         | A.7.26 IC_CLR_START_DET                                                                        | 349        |

| 3.14         | I.7.27 IC_CLR_GEN_CALL                                                                         | 349        |

| 3.14         | A.7.28 IC ENABLE.                                                                              | 350        |

| 3.14         | I.7.29 IC_STATUS                                                                               | 351        |

| 3.14         | 4.7.30 IC TXFLR                                                                                | 352        |

| 3 14         | 1.7.31 IC_RXFLR                                                                                | 352        |

|              | 4.7.321C SDA HOLD                                                                              |            |

|              | 4.7.33 IC TX ABRT SOURCE                                                                       |            |

|              | 4.7.34 IC_SLV_DATA_NACK_ONLY                                                                   |            |

|              | 1.7.351C DMA CR                                                                                |            |

|              |                                                                                                |            |

|              | 4.7.36IC_DMA_TDLR                                                                              |            |

|              | 4.7.37 IC DMA_RDLR                                                                             |            |

|              | 4.7.38IC_SDA_SETUP                                                                             |            |

|              | 1.7.39 IC_ACK_GENERAL_CALL                                                                     |            |

|              | 4.7.40 IC_ENABLE_STATUS                                                                        |            |

|              | 4.7.41 IC_FS_SPKLEN                                                                            |            |

|              | 1.7.42 IC_HS_SPKLEN                                                                            |            |

| 3.14         | 1.7.43 IC_CLR_RESTART_DET                                                                      | 361        |

| 3.14         | 1.7.44IC SCL STUCK AT LOW TIMEOUT                                                              | 361        |

| 3.14         | A.7.45 IC CLR SCL STUCK DET                                                                    | 361        |

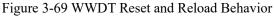

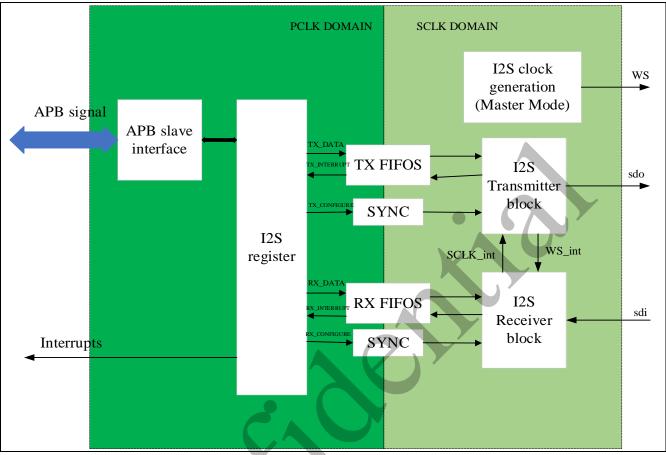

|              | C Sound (I2S)                                                                                  |            |

| 3.15.1       | Overview                                                                                       |            |

| 3.15.2       | Features                                                                                       |            |

| 3.15.3       | Block Diagram                                                                                  |            |

| 3.15.4       | Functional Description                                                                         |            |

|              | 5.4.1 I2S Enable                                                                               |            |

|              | 5.4.2 I2S Enable                                                                               |            |

| 5.15         |                                                                                                |            |

|              | Transmitter Block Enable                                                                       |            |

|              | Transmitter Channel Enable                                                                     |            |

|              | Transmit Channel Audio Data Resolution                                                         |            |

|              | Transmit Channel FIFO                                                                          |            |

|              | Transmit Channel Interrupts                                                                    | 367        |

|      | Writing to a Transmit Channel                                                                                                                                                |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

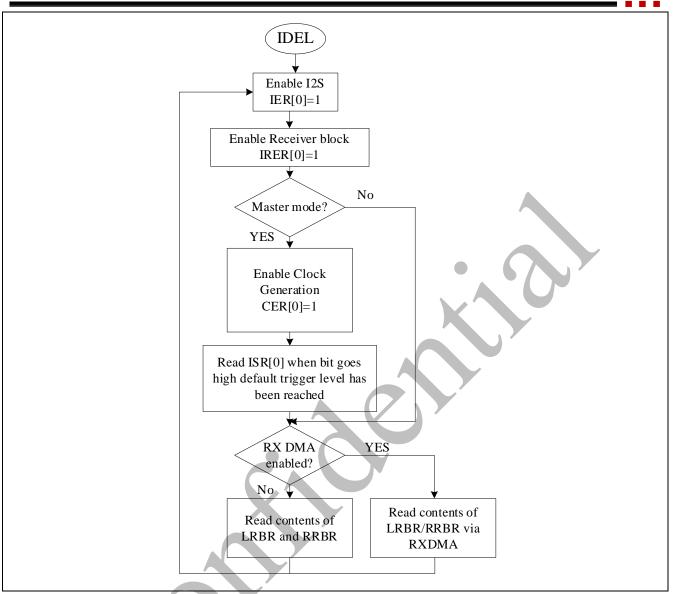

|      | 3.15.4.3 I2S as Receiver                                                                                                                                                     |     |

|      | Receiver Block Enable                                                                                                                                                        |     |

|      | Receive Channel Enable                                                                                                                                                       |     |

|      | Receive Channel Audio Data Resolution                                                                                                                                        |     |

|      | Receive Channel FIFO                                                                                                                                                         |     |

|      | Receive Channel Interrupts                                                                                                                                                   |     |

|      | Reading from a Receive Channel                                                                                                                                               |     |

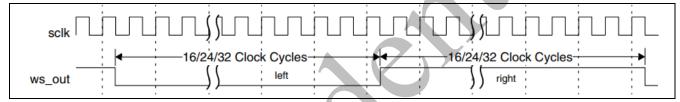

|      | 3.15.4.4 Clock Generation (Master Mode)                                                                                                                                      |     |

|      | Clock Generation Enable                                                                                                                                                      |     |

|      | Word Select Generation                                                                                                                                                       |     |

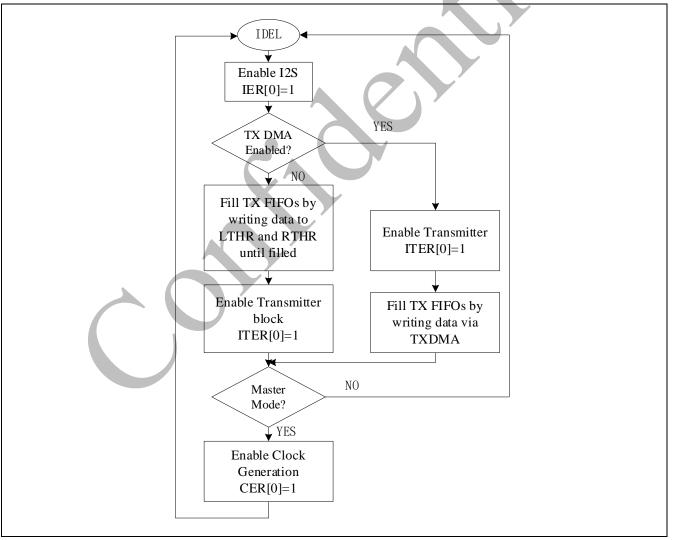

|      | 3.15.4.5 Programming I2S                                                                                                                                                     |     |

|      | Slave Mode                                                                                                                                                                   | 374 |

|      | Master Mode                                                                                                                                                                  |     |

|      | Single Channel transmit Mode                                                                                                                                                 |     |

|      | Single Channel receive Mode                                                                                                                                                  |     |

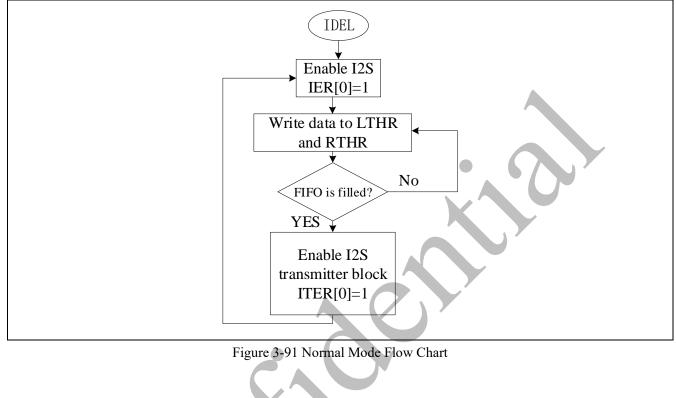

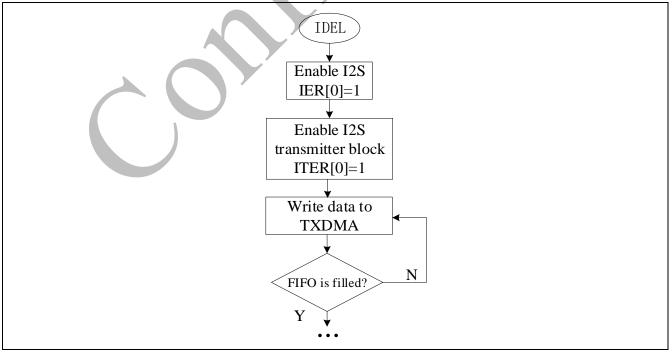

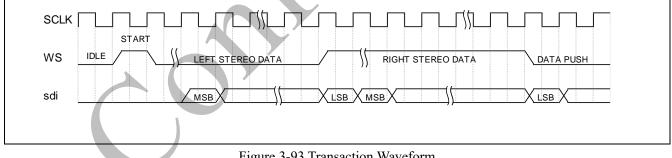

| 3    | .15.5 Transaction Example                                                                                                                                                    | 376 |

| -    | 15.6 I2S Register Map.                                                                                                                                                       |     |

|      | .15.6 I2S Register Map<br>15.7 I2S Register Description                                                                                                                      |     |

| 5.   | 2 15 7 1 128 Englisher Description                                                                                                                                           |     |

|      | 3.15.7.1 I2S Enable Register (IER)         3.15.7.2 I2S Receiver Block Enable Register (IRER)                                                                                |     |

|      | 3.15.7.2.125 Receiver Block Enable Register (IRER)                                                                                                                           |     |

|      | <ul> <li>3.15.7.3 I2S Transmitter Block Enable Register (ITER)</li> <li>3.15.7.4 Clock Enable Register (CER)</li> <li>3.15.7.5 Clock Configuration Register (CCR)</li> </ul> |     |

|      | 3.15.7.4 Clock Enable Register (CER)                                                                                                                                         |     |

|      | 3.15.7.5 Clock Configuration Register (CCR)                                                                                                                                  |     |

|      | 3.15.7.6 Receiver Block FIFO Reset Register (RXFFR)                                                                                                                          |     |

|      | 3.15.7.7 Transmitter Block FIFO Reset Register (TXFFR)                                                                                                                       |     |

|      | 3.15.7.8 Left Receive Buffer Register (LRBR)                                                                                                                                 |     |

|      | 3.15.7.9 Left Transmit Holding Register (LTHR)                                                                                                                               |     |

|      | 3.15.7.10 Right Receive Buffer Register (RRBR)                                                                                                                               |     |

|      | 3.15.7.11 Right Transmit Holding Register (RTHR)                                                                                                                             |     |

|      | 3.15.7.12 Receive Enable Register (RER)                                                                                                                                      |     |

|      | 3.15.7.13 Transmit Enable Register (TER)                                                                                                                                     |     |

|      | 3.15.7.14 Receive Configuration Register (RCR)                                                                                                                               |     |

|      | 3.15.7.15 Transmit Configuration Register (TCR)                                                                                                                              |     |

|      | 3.15.7.16 Interrupt Status Register (ISR)                                                                                                                                    |     |

|      | 3.15.7.17 Interrupt Mask Register (IMR)                                                                                                                                      |     |

|      | 3.15.7.18 Receive Overrun Register (ROR)                                                                                                                                     |     |

|      | 3.15.7.19 Transmit Overrun Register (TOR)                                                                                                                                    |     |

|      | 3.15.7.20 Receive FIFO Configuration Register (RFCR)                                                                                                                         |     |

|      | 3.15.7.21 Transmit FIFO Configuration Register (RFCR)                                                                                                                        |     |

|      | 3.15.7.22 Receive FIFO Flush Register (RFF)                                                                                                                                  |     |

|      | 3.15.7.23 Transmit FIFO Flush Register (TFF)                                                                                                                                 |     |

|      | 3.15.7.24 Receiver Block DMA Register (RXDMA)                                                                                                                                |     |

|      | 3.15.7.25 Transmitter Block DMA Register (TXDMA)                                                                                                                             |     |

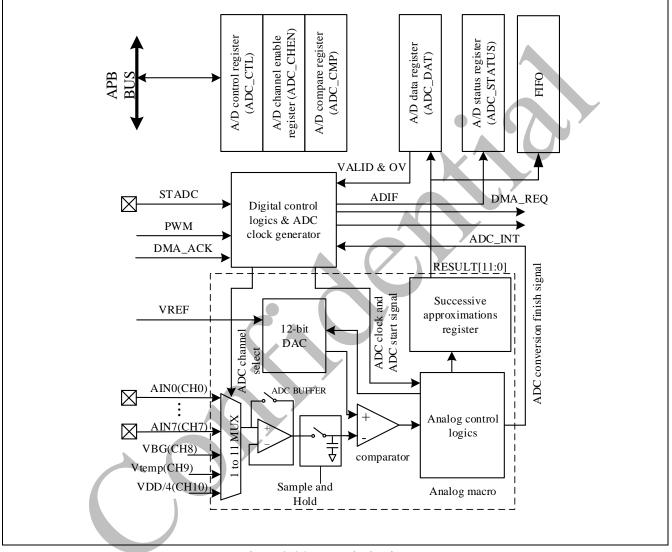

| 3.16 | Analog-to-Digital Converter (ADC)                                                                                                                                            |     |

| 3.   | 16.1 Overview                                                                                                                                                                |     |

| 3.   | .16.2 Features                                                                                                                                                               |     |

| 3.   | .16.3 Block Diagram                                                                                                                                                          |     |

|      | 16.4 Basic Configuration                                                                                                                                                     |     |

|      | 16.5 Functional Description                                                                                                                                                  |     |

| 5.   | 3.16.5.1 ADC Peripheral Clock Generator                                                                                                                                      |     |

|      | Temperature Sensor.                                                                                                                                                          |     |

|      | Battery detection                                                                                                                                                            |     |

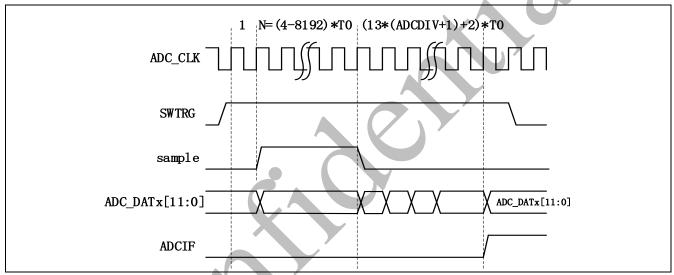

|      | 3.16.5.2 ADC Operation                                                                                                                                                       |     |

|      | 3.16.5.3 External Trigger Input Sampling and A/D Conversion Time                                                                                                             |     |

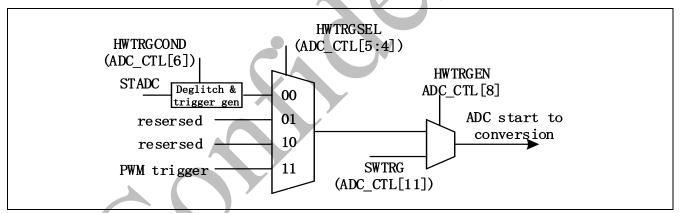

|      | 3.16.5.4 PWM Trigger                                                                                                                                                         |     |

|      |                                                                                                                                                                              |     |

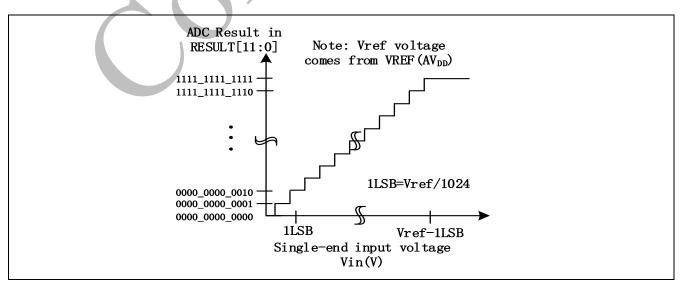

|       | 3.16.5.5 Conversion Result Monitor by Compare Mode Function                                                                                                              | 392 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

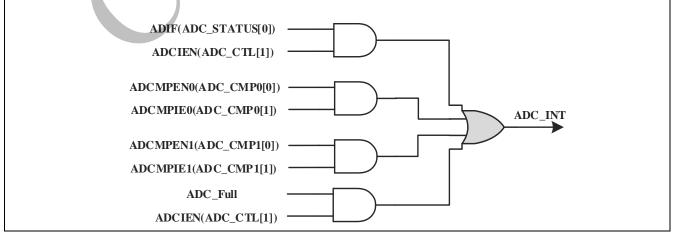

|       | 3.16.5.6 Interrupt Mode                                                                                                                                                  |     |

|       | 3.16.5.7 Polling Mode                                                                                                                                                    |     |

|       | 3.16.5.8 Shunt Mode                                                                                                                                                      |     |

|       | 3.16.5.9 PWM Sequential Mode                                                                                                                                             |     |

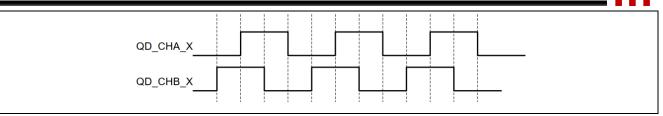

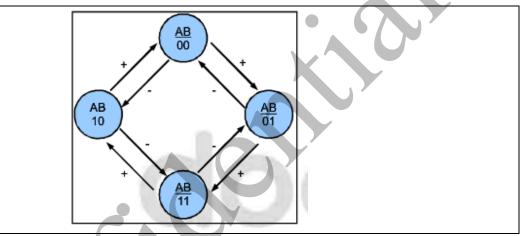

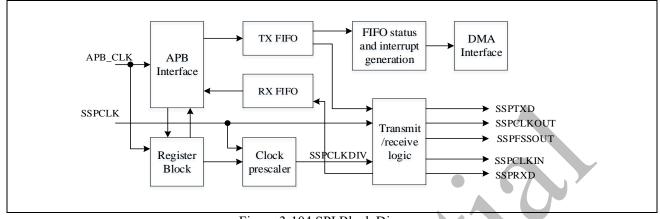

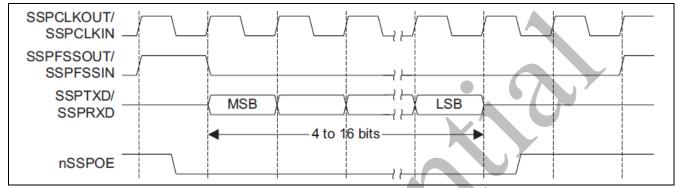

|       | 3.16.5.10 DMA Operation                                                                                                                                                  |     |