### PAN101x series

# User Manual

V1.1 Aug. 2024

Panchip Microelectronics Co., Ltd.

**BLE SoC Transceiver**

#### **General Description**

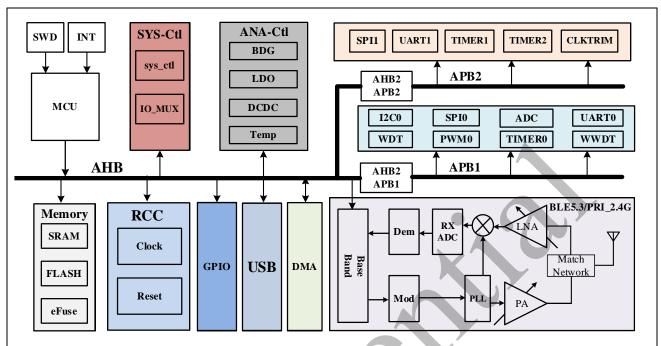

PAN101x series integrates BLE5.3 and 2.4GHz dual-mode wireless SoC transceiver. The transceiver works in the 2.400-2.483GHz universal ISM frequency band. There is a 256KB Flash program memory and a 16KB SRAM memory. In addition, PAN101x series is equipped with a wealth of peripherals, including up to 12 GPIOs, 8-channel PWM, one 32-bit timer, two 24-bit timers, one I2C, two UARTs, two SPIs, four external channels ADC, WDT, WWDT, USB2.0(Full Speed), 32K RC etc. PAN101x series is suitable for application of wireless mouse, smart home and electronic shelf label.

#### **Key Features**

- MCU

- 32-bit MCU core running up to 48MHz

- Memory

- 256KB flash supporting deep power-down mode

- 16KB SRAM

- 128B eFuse

- 4KB I-cache

- Low Power

- Active mode RX: 2.5mA@1Mbps(DCDC)

- Active mode TX at 0dBm: 5.06mA(DCDC)

- Standby mode: 0.28uA

- Standby mode(16K SRAM retention):

1.78uA (GPIO, XTL, RCL can wake up)

- Deep sleep mode: 3.37uA (All Logic Retention, GPIO, XTL, RCL can wake up)

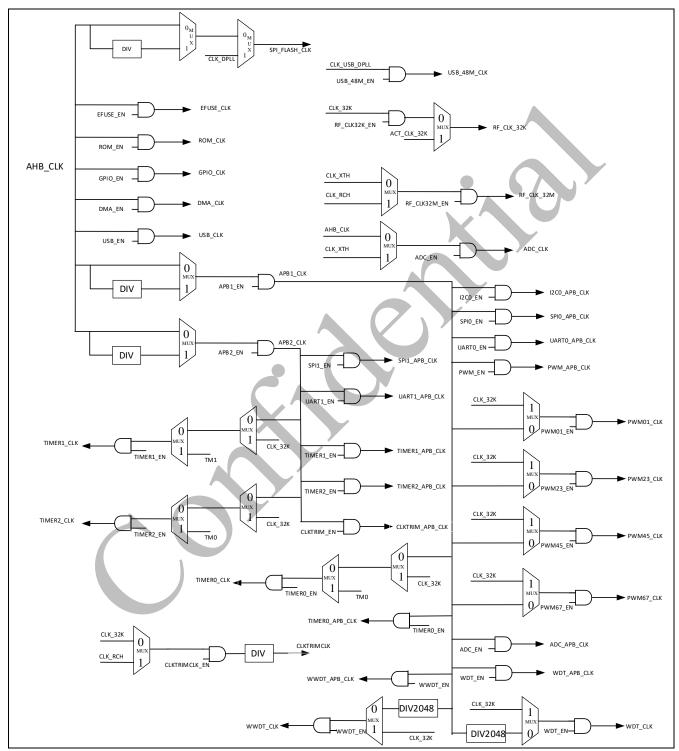

- Clock

- 32MHz RC

- 32MHz XTAL

- 32kHz RC

- 32.768kHz XTAL

- DPLL(48MHz)

- RF

- Mode

- BLE5.3 modes:

- 1Mbps, 2Mbps, 500kbps, 125kbps

- 2.4G private protocol:

1Mbps, 2Mbps 500kbps, 250kbps, 125kbps, supporting hardware ACK

- Output power: up to 8.5dBm

- Receiver

- -98dBm@125kbps

- -98dBm@500kbps

- -95dBm@1Mbps

- -92dBm@2Mbps

- RSSI

- Resolution: 0.25dB

- Accuracy: ±2dB

- Range: -90dbm  $\sim -15$ dBm

- Single antenna supported

- Safety regulations: BQB / ETSI / FCC

#### Peripheral

- Up to 12 GPIOs

- 8-channel PWM one 32-bit timer, two 24-bit timers

- One I2C

- Two UARTs

- Two SPIs

- 2-channel DMA

- 9-channel ADC (4 ext, VBG\_1P2, VBG\_VT, 1/4VDD, VBG 0P6, Temp2)

- WDT/WWDT

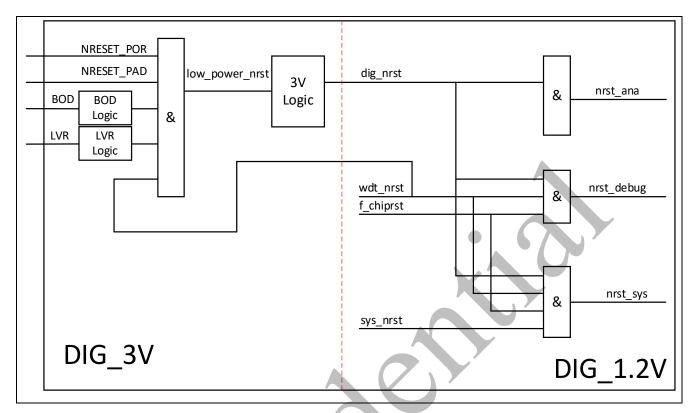

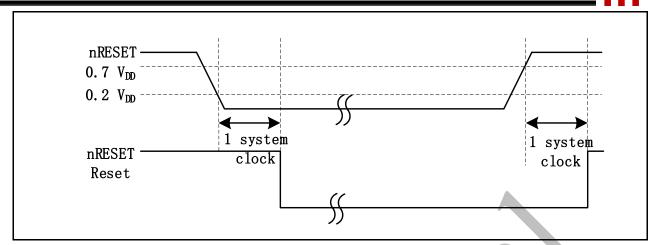

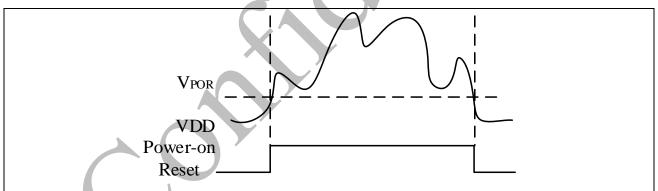

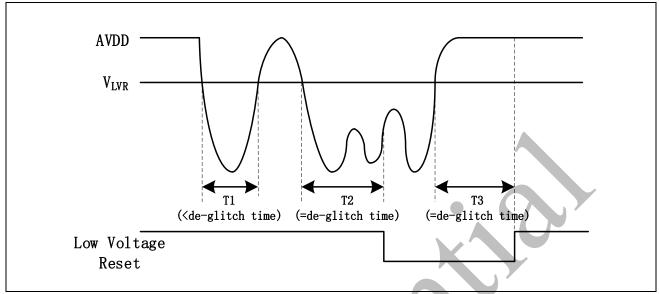

- IO / BOD / POR / LVR / System reset

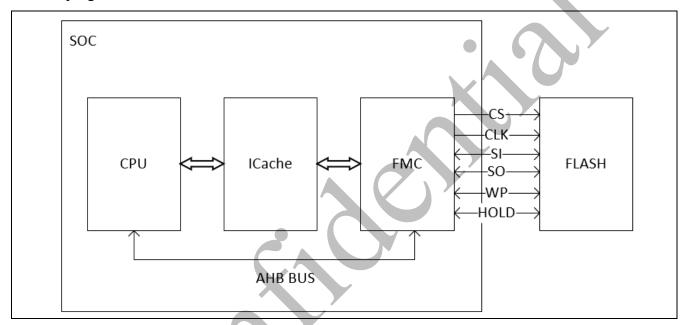

- FMC(Support IAP, support the boot loader with address 0x0)

- Clock measurement and clock calibration

- USB2.0(Full speed)

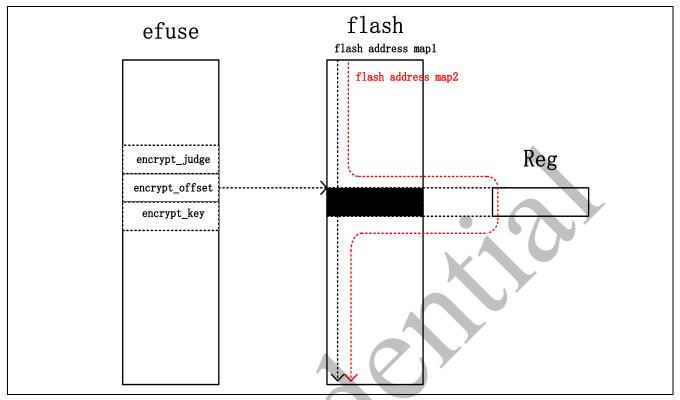

- Flash data encryption

#### Temperature sensor

Support temperature sensor

- Test range:  $-40^{\circ}$ C  $\sim 85^{\circ}$ C

#### Power Management

- Integrated voltage regulator

- Operating voltage: 1.8V to 3.6V (Support DCDC)

- Package

- SSOP24 / MSOP10

#### • Operating Condition

- Operating temperature:  $-40^{\circ}\text{C} \sim 85^{\circ}\text{C}$

- Storage temperature: -60°C~150°C

### **Typical Applications**

- Electronic Shelf Label

- Wireless mouse

- LED light control

#### **Bluetooth Features**

#### **Bluetooth Low Energy Controller**

The PAN101x series Bluetooth Low Energy Controller supports all low-energy features required by Bluetooth specification version 5.3. The controller supports the following:

- Support 1M PHY, 2M PHY and Coded PHY (s2 and s8)

- Support Advertising, and Connection and Peripheral role

- Up to 2 Link Layer state machines concurrently:

- Advertising

- Connection

- Support LE Features:

- LL Encryption

- LE Data Packet Length Extension

- Channel Selection Algorithm #2

- Constant Tone Extension

- Support Update Channel Statistics

#### **Bluetooth Host**

- Generic Access Profile (GAP) with all possible LE roles

- Peripheral

- Broadcaster

- GATT (Generic Attribute Profile)

- Server (to be a sensor)

- Client (to connect to sensors)

- Pairing support, including the Secure Connections feature from Bluetooth 4.2

- Non-volatile storage support for permanent storage of Bluetooth-specific settings and data

- Clean HCI driver abstraction

- 3-Wire (H5) & 5-Wire (H4) UART

- SPI

- Local controller support as a virtual HCI driver

#### **Proprietary Radio 2.4G Features**

- Support 250K, 1M and 2M PHY

- XN297L, PAN1026 protocol compliant

- Support No Acknowledge, Acknowledge and Acknowledge with payload

- Support CRC8, CRC16 and CRC24

- Support whitening

- Compatible with Bluetooth frame structure, can simulate Bluetooth broadcast and scanning

- Compatible with Bluetooth Coded PHY S2/S8

- Supports 2-byte address

- Support the same spread spectrum function as the BLE protocol

### Content

| Ge  | neral D | scription                                                     | 2  |

|-----|---------|---------------------------------------------------------------|----|

|     |         | 2S                                                            |    |

|     |         | olications                                                    |    |

|     |         | eatures                                                       |    |

|     |         | ooth Low Energy Controller                                    |    |

|     |         | ooth Host                                                     |    |

| Pro | prietar | Radio 2.4G Features                                           | 3  |

| Co  | ntent   | <u></u>                                                       | 4  |

| 1   | Bloc    | Diagram                                                       | 23 |

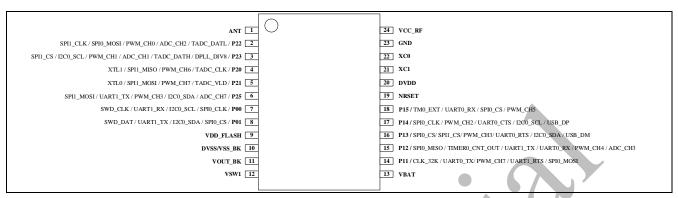

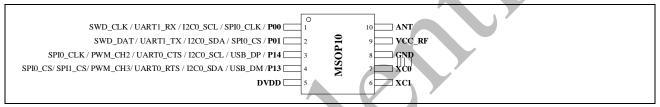

| 2   | Pin I   | ormation                                                      | 24 |

|     | 2.1     | Pin Diagram                                                   |    |

|     | 2.2     | Pin Descriptions                                              | 25 |

| 3   | Func    | on Description                                                | 28 |

|     | 3.1     | System Manager                                                |    |

|     |         | 3.1.1 Overview                                                |    |

|     |         | 3.1.2 Memory Organization                                     |    |

|     |         | 3.1.2.1 Overview                                              |    |

|     |         | 3.1.2.2 System Memory Map                                     |    |

|     |         | 3.1.3 System Register Map                                     |    |

|     |         | 3.1.4 System Register Description                             |    |

|     |         | 3.1.4.1 Multiple Function Port0 Control Register (SYS_P0_MFP) |    |

|     |         | 3.1.4.2 Multiple Function Port1 Control Register (SYS_P1_MFP) |    |

|     |         | 3.1.4.3 Multiple Function Port2 Control Register (SYS_P2_MFP) |    |

|     |         | 3.1.4.4 SYS_REGLCTL                                           |    |

|     |         | 3.1.4.5 SYS_STATUS                                            |    |

|     |         | 3.1.4.6 SYS_CTRL0                                             |    |

|     |         | 3.1.4.7 SYS_CTRL1                                             | 36 |

|     |         | 3.1.5 System Timer (SysTick)                                  |    |

|     |         | 3.1.5.1 System Timer Control Register Map                     |    |

|     |         | 3.1.5.2 System Timer Control Register Description             |    |

|     |         | SysTick Control and Status Register (SYST_CTRL)               |    |

|     |         | SysTick Reload Value Register (SYST_LOAD)                     |    |

|     |         | SysTick Current Value Register (SYST_VAL)                     |    |

|     |         | Nested Vectored Interrupt Controller (NVIC)                   |    |

|     |         | 3.1.6.1 Overview                                              |    |

|     |         | 3.1.6.2 Features                                              |    |

|     |         | 3.1.6.3 Exception Model and System Interrupt Map              |    |

|     |         | 3.1.6.4 Vector Table                                          |    |

|     |         | 3.1.6.5 Operation Description                                 |    |

|     |         | 3.1.6.6 NVIC Control Register Map                             |    |

|     |         | 3.1.6.7 NVIC Control Register Description                     |    |

|     |         | IRQ0 ~ IRQ31 Set-Enable Control Register (NVIC_ISER)          |    |

|     |         | IRQ0 ~ IRQ31 Clear-Enable Control Register (NVIC_ICER)        |    |

|     |         | IRQ0 ~ IRQ31 Set-Fending Control Register (NVIC_ISFR)         |    |

|     |         | IRQ0 ~ IRQ3 Interrupt Priority Register (NVIC_ICPR)           |    |

|     |         | IRQ4 ~ IRQ7 Interrupt Priority Register (NVIC_IPR0)           |    |

|     |         | IRQ4 ~ IRQ7 Interrupt Priority Register (INVIC_IPR1)          |    |

|     |         | IRQ12 ~ IRQ15 Interrupt Priority Register (NVIC_IPR2)         |    |

|     |         | IRQ16 ~ IRQ19 Interrupt Priority Register (NVIC_IPR9)         |    |

|     |         | IRQ20 ~ IRQ23 Interrupt Priority Register (NVIC_IPR5)         |    |

|     |         | IRQ24 ~ IRQ27 Interrupt Priority Register (NVIC IPR6)         |    |

|     |         |                                                               |    |

|     |         | TROOP TROOP IN THE PARTY OF THE PROPERTY OF TH | 40         |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|     |         | IRQ28 ~ IRQ31 Interrupt Priority Register (NVIC_IPR7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |

|     |         | .1.6.8 System Control Block Registers (SCB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

|     | 3.      | .1.6.9 System Control Block Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50         |

|     | 3.      | .1.6.10 System Control Block Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50         |

|     |         | CPUID Base Register (SCS CPUID)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50         |

|     |         | Interrupt Control State Register (SCS_ICSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

|     |         | Application Interrupt and Reset Control Register (SCS_AIRCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |

|     |         | System Control Register (SCS SCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

|     |         | System Handler Priority Register 2 (SCS SHPR2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

|     |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| 2.2 | ъ       | System Handler Priority Register 3 (SCS_SHPR3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

| 3.2 |         | ver Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

|     | 3.2.1   | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54         |

|     | 3.2.2   | System Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 54         |

|     | 3.      | .2.2.1 Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 54         |

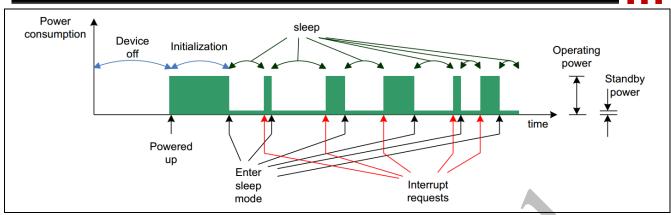

|     | 3.2.3   | Low Power System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 54         |

|     | 3.      | .2.3.1 Low power system introduction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 54         |

|     | 3       | .2.3.2 Low Power Mode of MCU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55         |

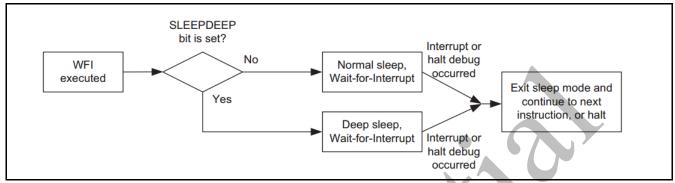

|     | ٥.      | Sleen Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 55<br>55   |

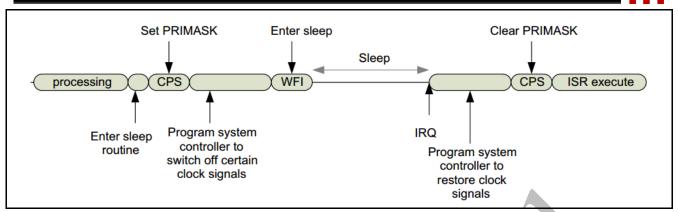

|     |         | Sleep ModeWFI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55         |

|     |         | W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50         |

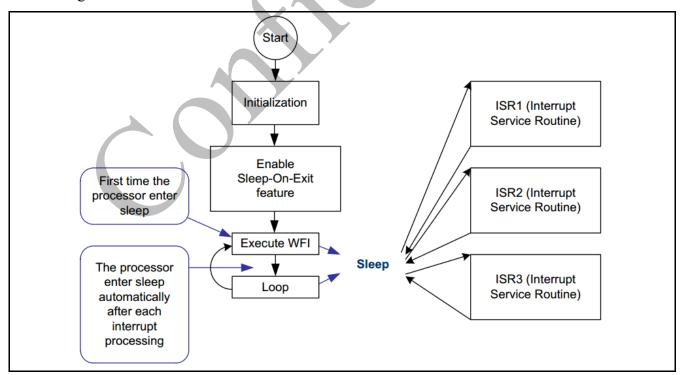

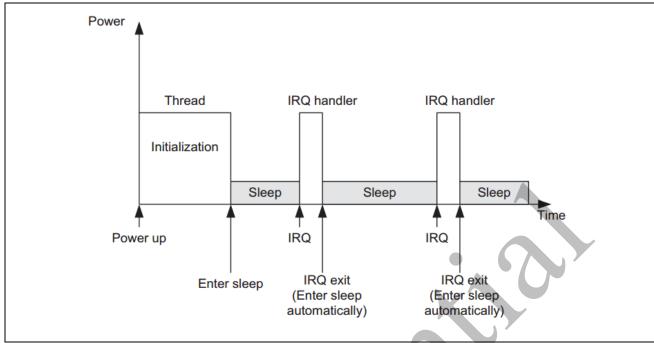

|     | 2 2 4   | Sleep-On-Exit Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5 /        |

|     | 3.2.4   | Low Power Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            |

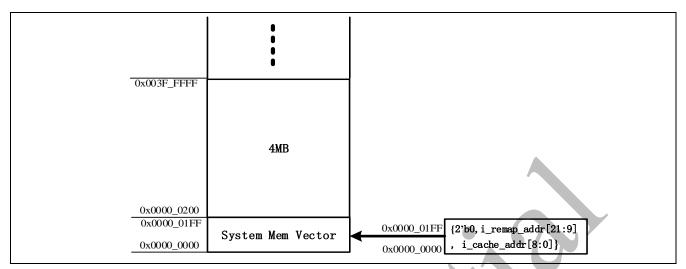

|     | 3.2.5   | Cpu Vector Table Remap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 59         |

|     | 3.2.6   | Cpu Vector Table Remap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 59         |

|     | 3.2.7   | FLASH Low Power Config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 60         |

|     | 3.2.8   | Register Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 61         |

|     | 3.2.9   | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 62         |

|     |         | .2.9.1 LP_REG_SYNC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 62         |

|     | 3       | .2.9.2 LP_FL_CTRL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 63         |

|     | 3.      | .2.9.3 LP_SPACING_TIME0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65<br>65   |

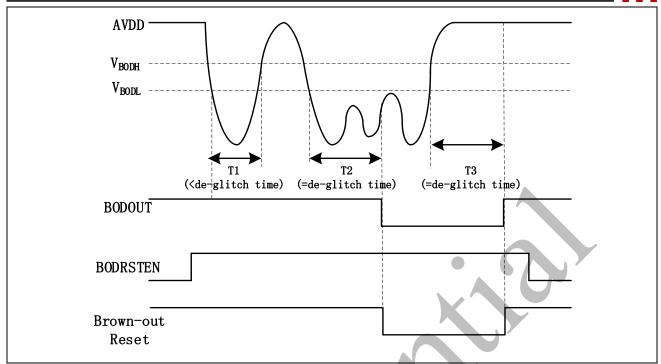

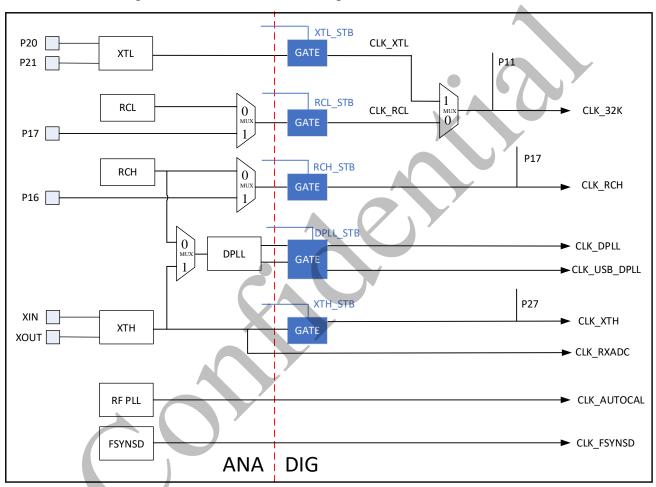

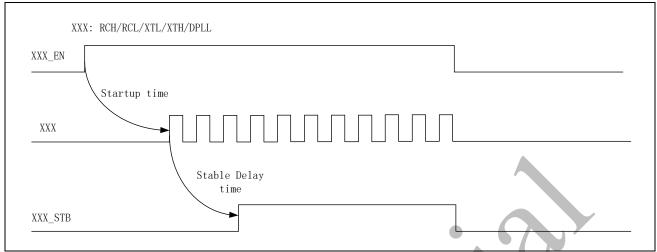

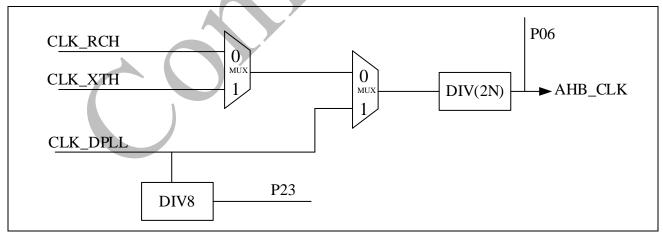

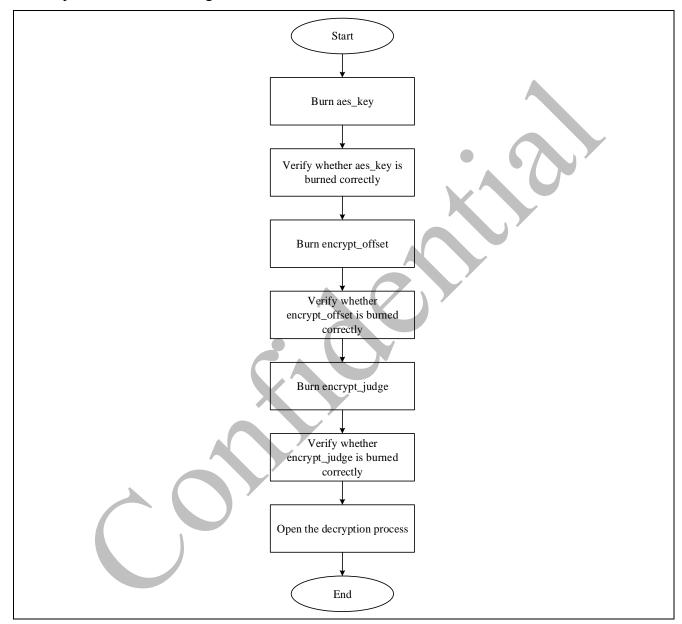

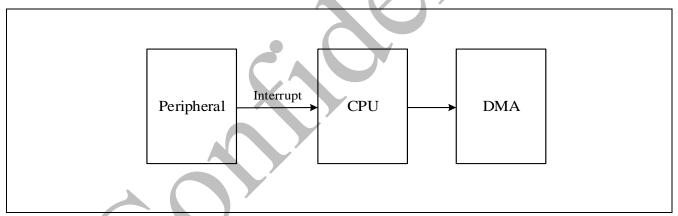

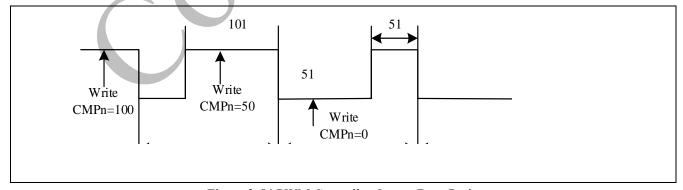

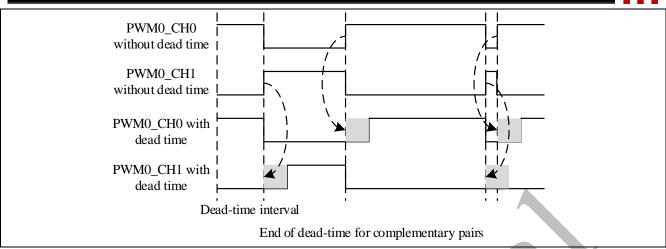

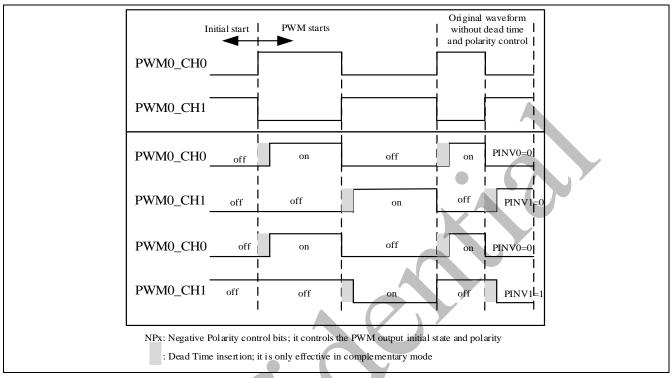

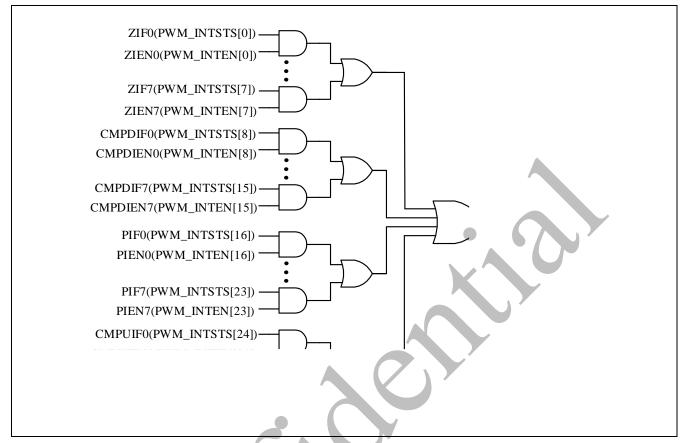

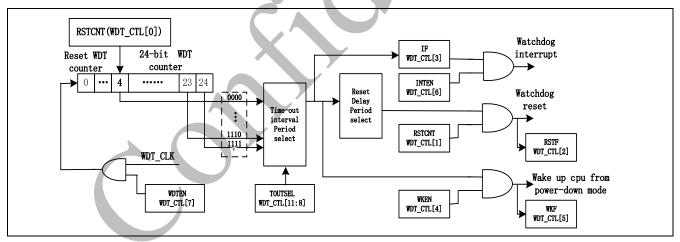

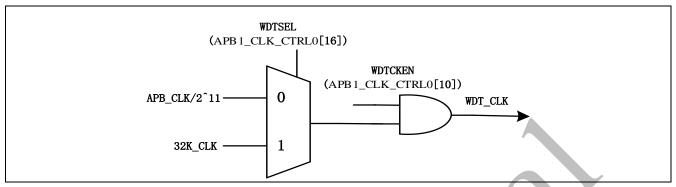

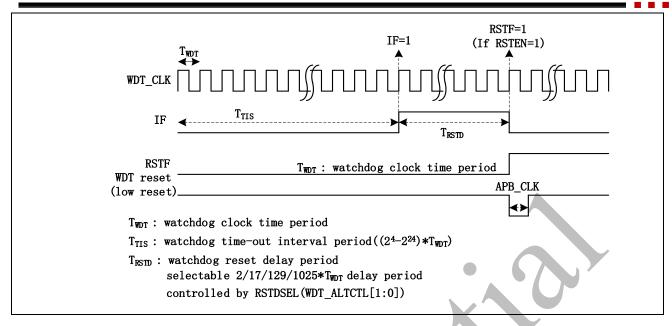

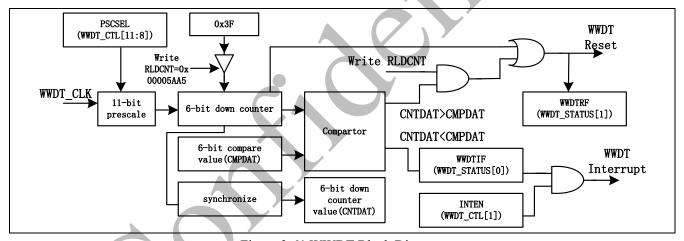

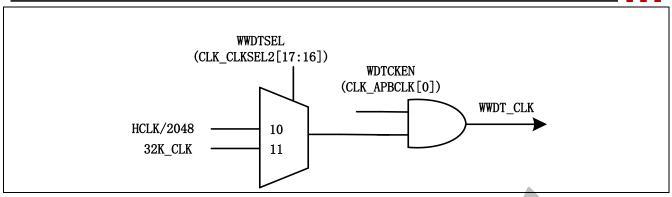

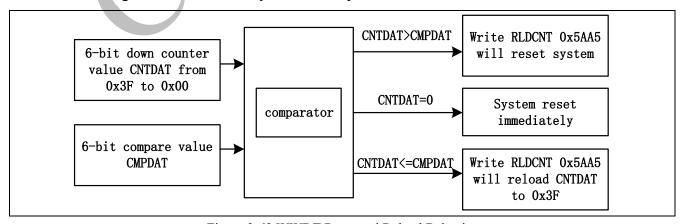

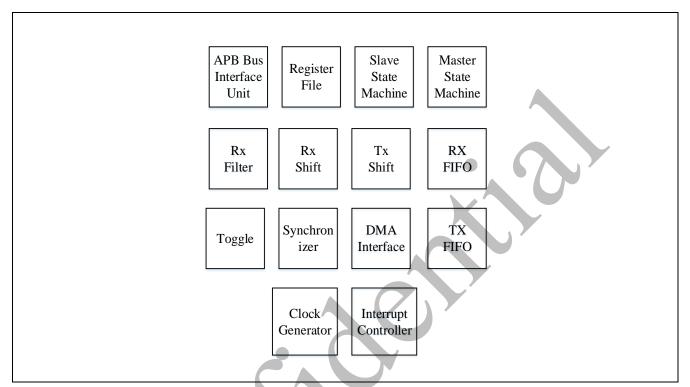

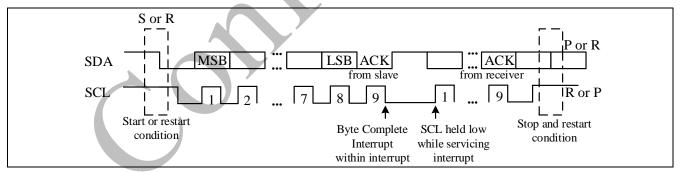

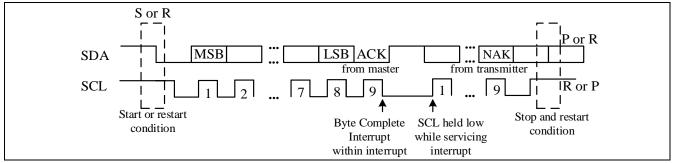

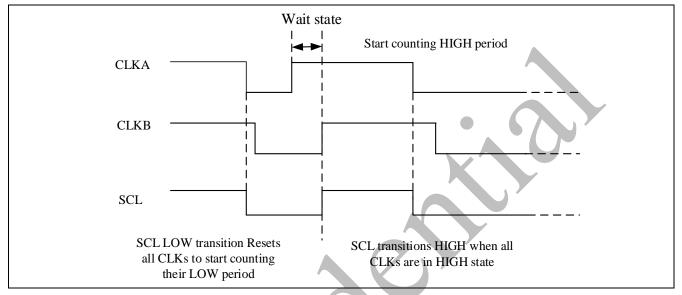

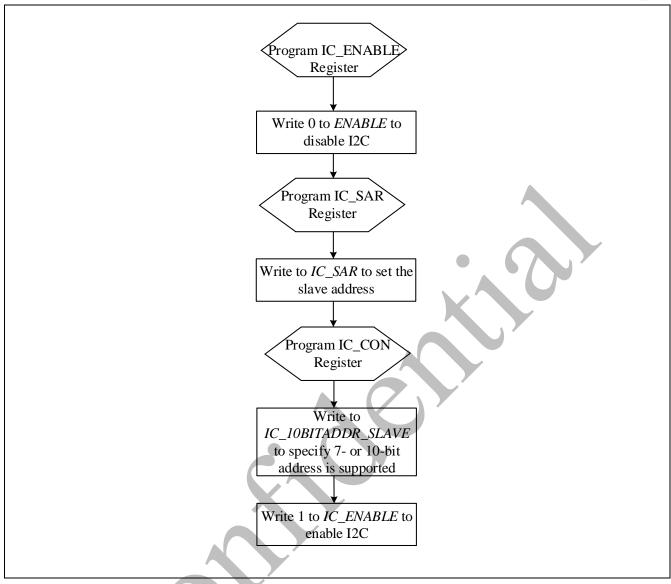

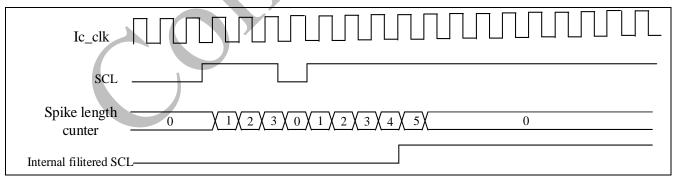

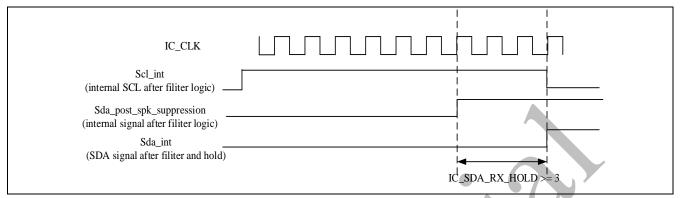

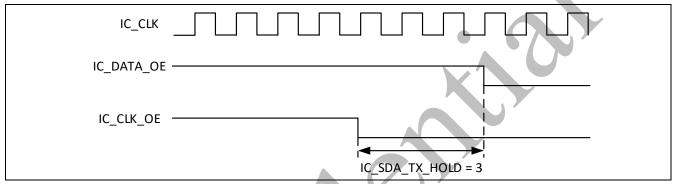

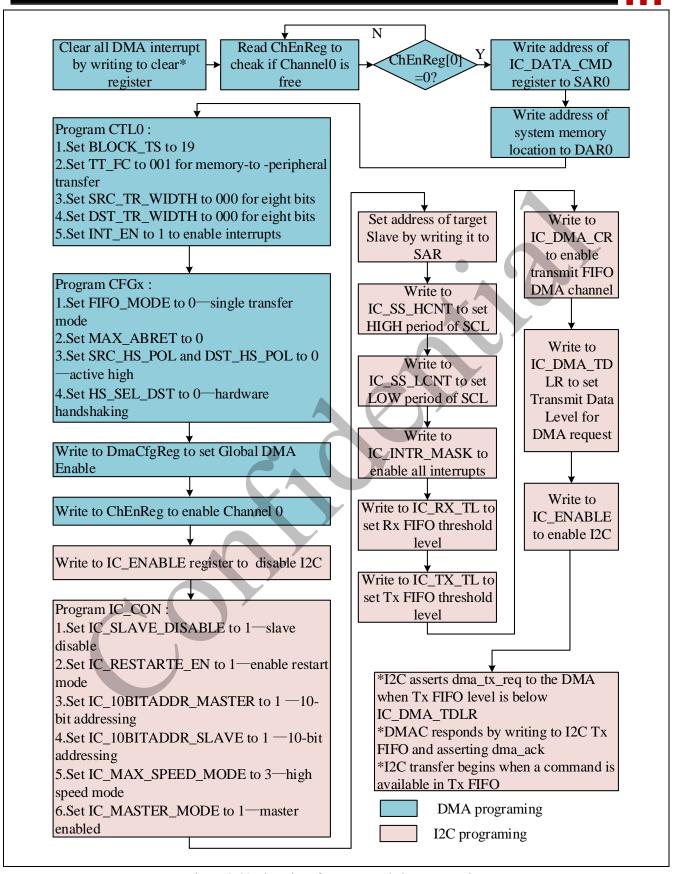

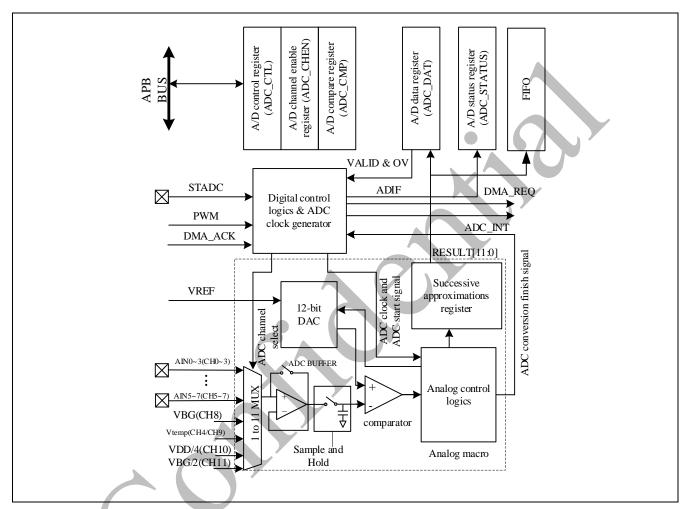

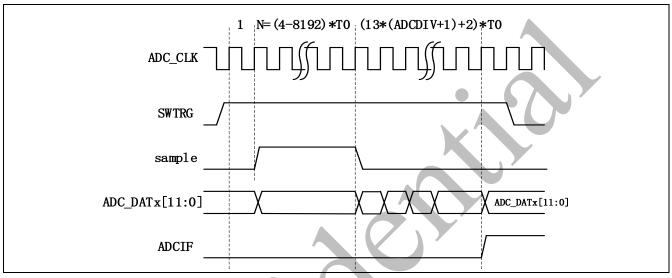

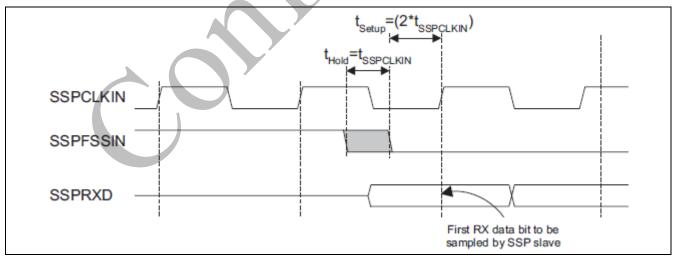

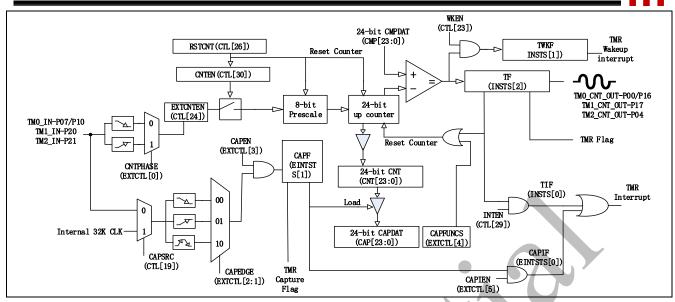

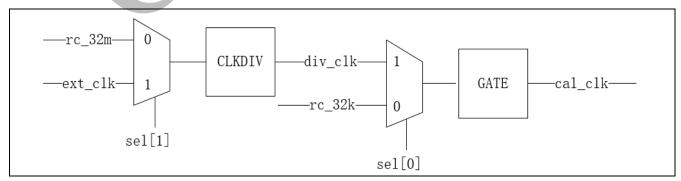

|     | 3.      | 2.9.4LP_SPACING_TIME1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 65         |